工具/软件:

您好:

我正在考虑使用 UCC24612-2。

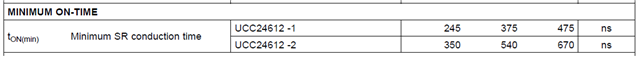

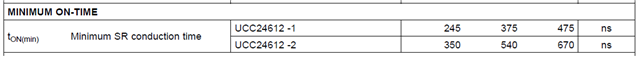

该 IC 具有 540ns(持续–2)的 TON 消隐未检测时间、以防止振铃达到关断阈值并导致栅极过早关断。

这种计数在什么时候开始?

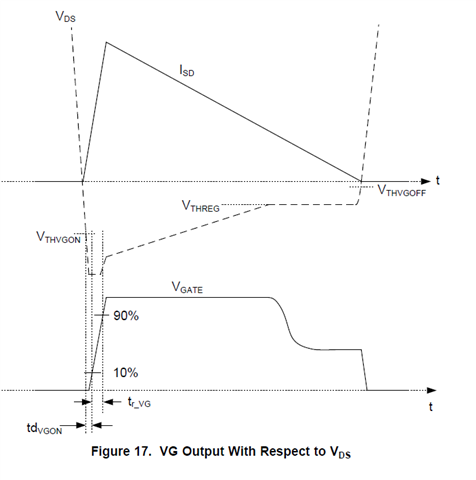

在栅极上升之前、存在 td VGON (170ns) 和 tr_VG (32ns) 的延迟。 它是否会在该操作结束后启动?

还是从 VDS 反转(电流开始流动的那一刻)开始?

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好:

我正在考虑使用 UCC24612-2。

该 IC 具有 540ns(持续–2)的 TON 消隐未检测时间、以防止振铃达到关断阈值并导致栅极过早关断。

这种计数在什么时候开始?

在栅极上升之前、存在 td VGON (170ns) 和 tr_VG (32ns) 的延迟。 它是否会在该操作结束后启动?

还是从 VDS 反转(电流开始流动的那一刻)开始?

此致、

你好、Kaji-San、

这是一个好问题。

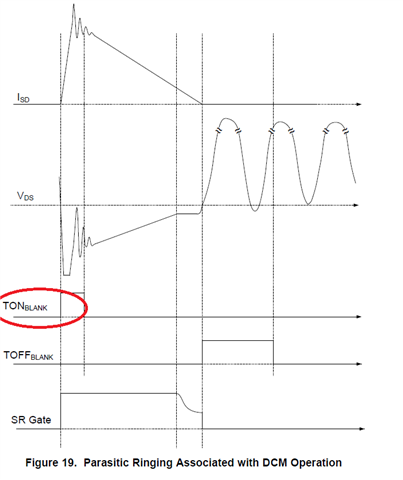

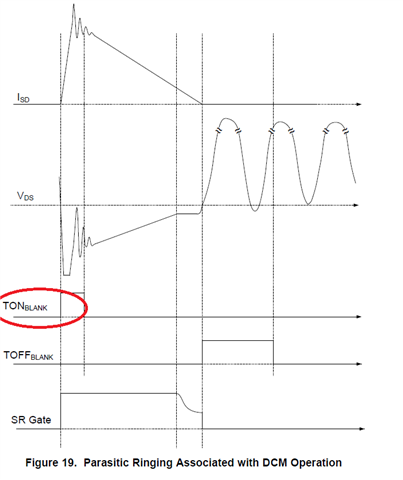

图 19 表示、 TON 消隐计时器在驱动 VG 输出的同一时刻启动(从 0V 开始、而不是从 10%上升点开始)。

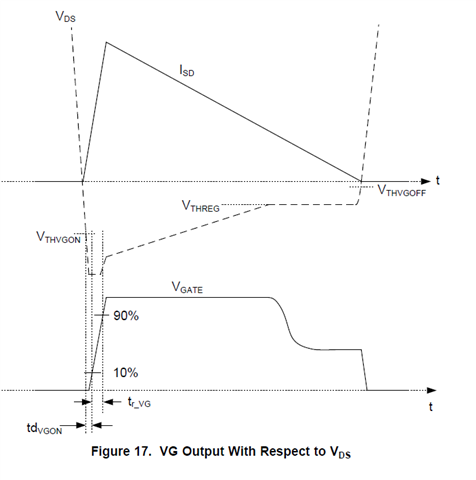

这进一步意味着自 Vds 超过 V_THVGON 导通阈值–0.24V 之时以来、导通延迟 TD_VGON (170ns) 已经过去。

我认为该时序不涉及 tr_VG(32ns 上升时间)。

这是我对数据表信息的解释。

我将与设计工程团队核实我的解释是否正确、但可能需要一两天时间才能得到答复。

此致、

Ulrich

感谢您的答复。

我收到了客户提供的其他信息。

如随附图所示、在 VD 引脚中插入一个二极管和电阻器可以改善症状、但这并不完全。

VD 引脚似乎受噪声的影响。

您能告诉我、是否有适当的方法来滤除 VD 引脚上的噪声?

另外、附图中的浅蓝色是栅极波形、电压似乎在逐渐下降。

这种正常运行吗?

如果您知道电压下降的原因、请告诉我。

此致、

你好、Kaji-San、

感谢您提供波形和原理图。 这解释了您询问消隐时序的原因。

栅极驱动电压具有逐渐下降的特性是正常情况。 它旨在减少到更接近 Vgs 阈值、以在 SR 导通时间结束时加快关断。 但是、交替的短/长导通时间会使控制器混淆、因此它无法找到一致的工作点。

噪声/振铃问题解决后、栅极驱动波形将更加一致。

绿色波形被识别为“SRFET ID“(即 SR FET 的漏极电流)、但不清楚是仅 Q201 中的电流、仅 Q208 中的电流、还是两个 FET 中的电流一起 、但不包括 R-C 缓冲器和 D211 、还是实际上是从引脚 8、9、10 处变压器绕组流出的总电流。

然而、这种高频电流振铃很可能涉及与绕组电容和 SR 电路电容谐振的次级绕组漏电感。

SR 控制器可检测 VD 输入端的负电压以导通、并且从源极到漏极会有足够的电流、从而通过体二极管(和并联 D211)产生负 VDS。 但振铃电流会在任何杂散电感上产生振铃电压、我怀疑两个 SR MOSFET Q201 和 Q208 采用 TO-220 或 TO-247 型封装、其中源极和漏极桥臂具有这样的电感。

R-C 缓冲器 R210+C204+C205 可能无法优化以快速抑制电压振铃(由于电流振铃)。

请让您的客户研究 R-C 缓冲器设计、以便更有效地缓冲振铃。 如果这些元件本身具有杂散电感、它们可能无法有效抑制振铃。

如果可能、可以重新设计变压器以减少漏电感、这会增加振铃频率、减少振铃能量并加快抑制速度(由于较高的交流电阻)、从而缩短振铃时间。 此外、我建议研究在变压器绕组输出上放置铁氧体磁珠是否也会加速振铃抑制、以便在导通消隐时间内消除。

我认为 VD 引脚上的(二极管+150R)||1.5kR 组合可能部分有效、因为它利用了 UCC24612 封装上的一些寄生引脚电容。 该引脚电容可能只有几个 pF、但该网络的 R-C 时间常数可能略微足够、从而有时将振铃降低到足以在消隐时间内下降并实现完全栅极驱动。

这表明额外的外部电容(放置在 VD 到 VS 之间)可以更好地滤除电压。 但是、这也增加了导通延迟时间、使其比 UCC24612-2 控制器中现有的 170ns 更长。

我不知道为什么应用了(二极管+150R)组合。 在 SR 导通(VDS 变为负值)时、二极管的极性使有效串联电阻= 150|1500 = 136R、因此 R-C 时间常数可能= 136R * 3pF =~409ns。 那么关断时+0.5V 检测的延迟为 1500R*3pF =~4500ns = 4.5us。

我建议移除 VD 网络的 (DIODE+150R) 部分、并将 1500R 电阻器的值更改为 300R、470R 或 680R 等、以检查哪个值能够可靠地消除振铃影响、同时不会引入过多的额外导通延迟。

但是、我认为首先减少振铃是一个更好的做法、而不是简单地用较长的时间延迟来阻止现有的振铃。

此致、

Ulrich

你好、Kaji-San、

以下是我们的设计工程部门的回复:

“ VD 引脚 【必须】始终低于–0.24V(导通阈值)、以便导通传播延迟计时器到期。 假设处于中间位置、VD 从–0.24V 上升至–0.05V、则 170ns 延迟将复位。

540ns 更像是最短导通时间。 一旦器件决定为该周期导通、对于 UCC24612-2、最小脉冲宽度为 540ns。 因此、一旦 170ns 到期、如果 VD 始终低于–0.24V、则器件决定导通、此时(170ns 完成后)已设置锁存器。 从此时起、脉冲最小为 540ns。'

UCC24612-1 的工作方式相同、但时序值较短 (80ns 和 375ns)。

此致、

Ulrich