工具/软件:

您好!

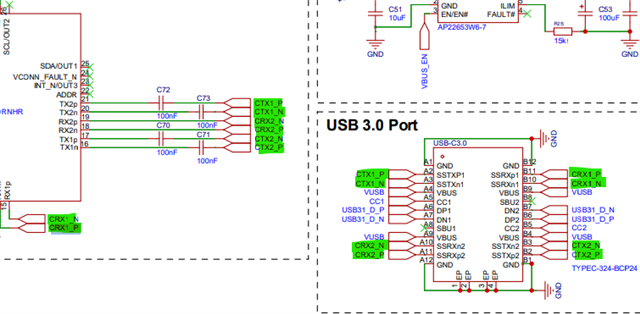

针对上一个主题、我更新了以代替建议的更改、只是希望在制造前审阅原理图和布局。

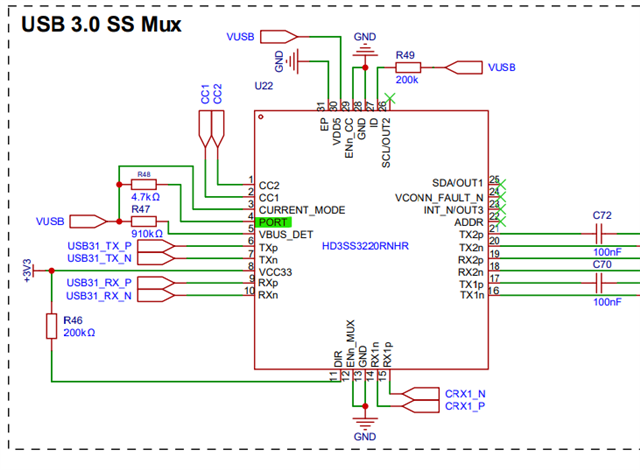

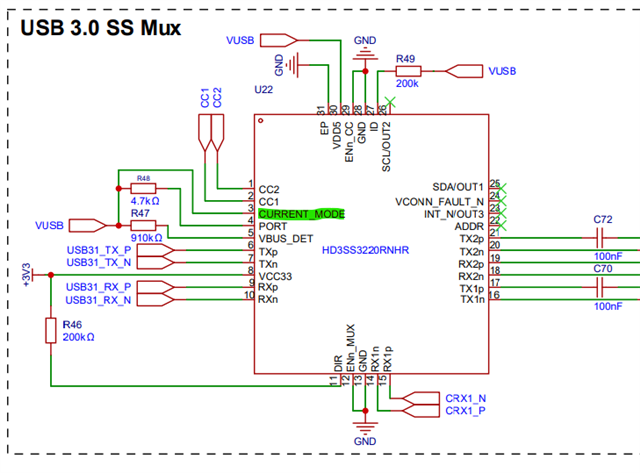

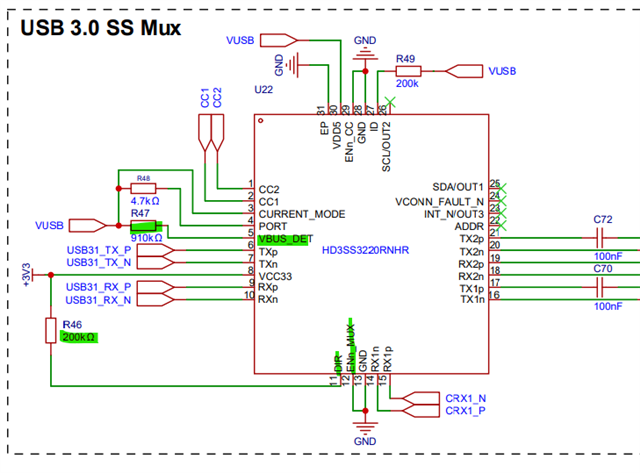

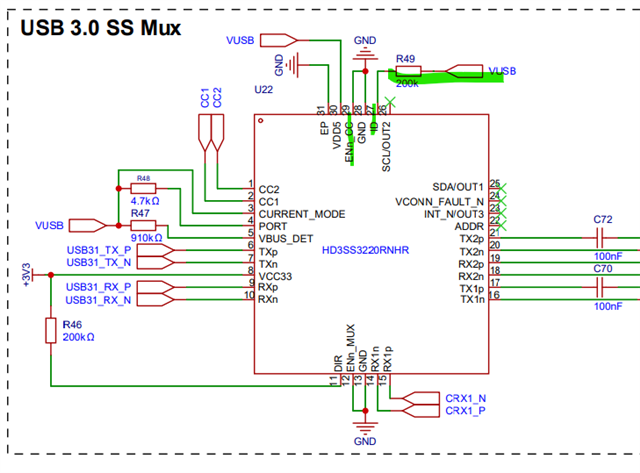

原理图:

布局:

第 1 层:

内层:

底层

PCB 有 6 层:

SIG/GND:GND:SIG/PWR:PWR:GND:SIG/GND

所有信号层都有接地电源、但为了更易于阅读、我已将其从视图中删除。 非常感谢对原理图和布局以及 USB-C 端口电源的反馈!

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好!

针对上一个主题、我更新了以代替建议的更改、只是希望在制造前审阅原理图和布局。

原理图:

布局:

第 1 层:

内层:

底层

PCB 有 6 层:

SIG/GND:GND:SIG/PWR:PWR:GND:SIG/GND

所有信号层都有接地电源、但为了更易于阅读、我已将其从视图中删除。 非常感谢对原理图和布局以及 USB-C 端口电源的反馈!

谢谢

您好!

遗憾的是、这是在 easyeda pro 中完成的、但我根据要求附上了原理图 pdf。 我将尝试以 Altium 格式导出、但请注意、它存在导出问题、因此不一定会反映实际设计、并且电路板轮廓和一些多边形覆铜会有一些伪影。

e2e.ti.com/.../Argo_2D00_v0.2.pdf

e2e.ti.com/.../Altium_5F00_Argo_2D00_v2_5F00_2025_2D00_09_2D00_10.zip

您好、

以下是原理图审阅:

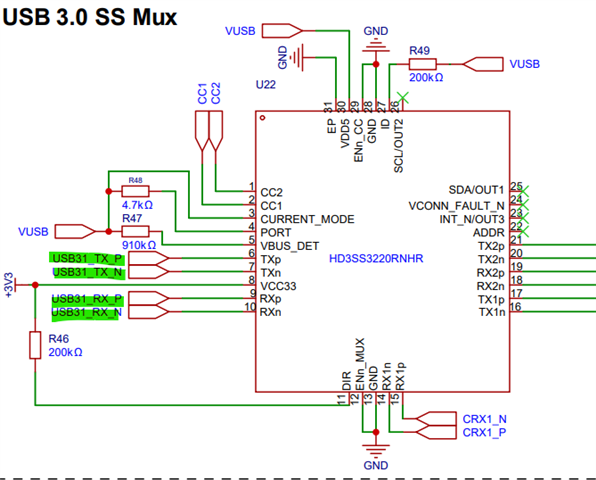

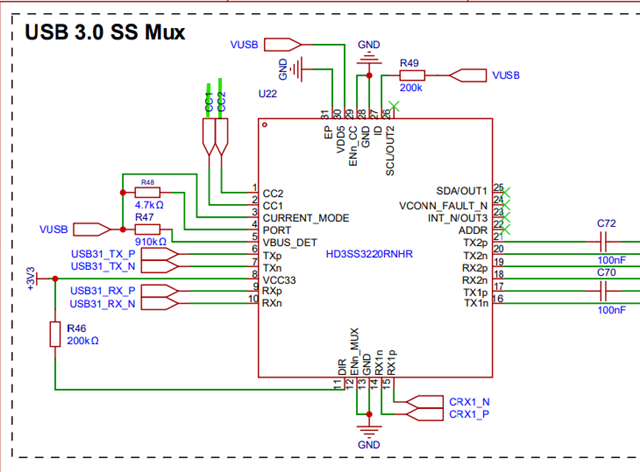

1) 多路复用器中公共路径的交流耦合状态是什么。 我看到这连接到外部连接器、但在该总线上没有看到任何交流耦合。

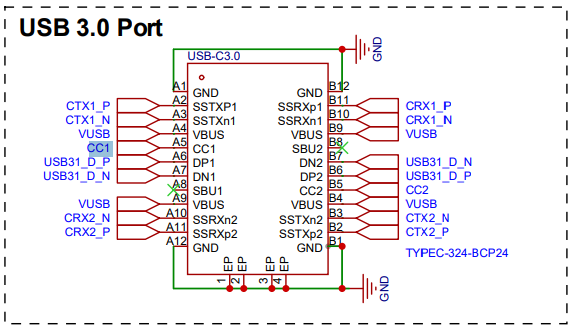

2) CC 引脚连接到两个 USB Type-C 连接器。 这不正确。 每个 PD Type-C 端口将需要一个 CC/USB 控制器。

HD3SS3220 的 CC 连接应仅连接到 USB3.0 Type-C 端口。

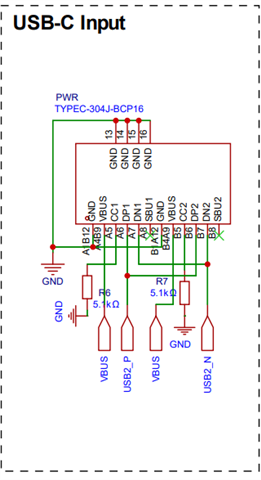

根据我的理解,每个诗人的功能是不同的。 USB Type-C 输入用于为电路板供电并以 USB 2.0 速度进行通信。 在本例中、正常和翻转方向的 DP 和 DN 连接在一起。 在这种情况下、您可以使用 CC PUP 和 PDOWN 网络、而不是 CC 控制器、因为翻转方向无关紧要。

1) 我建议将 PORT 引脚悬空以支持 DFP 和 UFP 运行。 这将使电路板的使用更加灵活。

4) 看起来此实现的电压为 5V 3A。 在这种情况下、使用 10K 电阻器将 CURRENT_MODE 引脚连接到 VCC。 不是直接连接。

5) VBUSDET 引脚具有 900K 的 VBUS、正常

DIR 引脚具有 200k PUP、但未连接到任何 SoC。 该 DIR 引脚将提供连接的翻转状态。 RPi SoC 可能需要该信号。

EN_MUX 直接接地

6) ENn_CC 直接接地、正常

ID 引脚具有 200k PUP、但该信号不会发送到 SoC。 此 ID 引脚通常用于告诉 SoC、当端口处于 DFP 模式时、设备已连接。 该引脚还可用作为 Vbus 供电的触发器。 RPi SoC 是否需要该信号?

7) 输出 USB Type-C 连接看起来正常。 TX 信号上为 100nF、RX 信号上直接连接。 可能有必要在此连接器上使用 ESD 二极管来保护此 PCB 上的 IC。 我们建议使用 PUSB3FR4。

大家好、非常感谢 Vishesh Pithadiya

1) 这直接连接到 Raspberry PI CM5 RX 和 TX 线路。我不确定它是否具有内置交流耦合、但官方 CM5 IO 板不包含任何(尽管它使用常规 USB-A 3.0 端口)

2) 我不确定自己的错误到底是什么。 多路复用器的 CC 线路只能连接到单个 USB-C 端口、另一个端口具有 5.1k 电阻器、与此设计或原理图无关、它只是器件上的标记、但根本没有电气连接。

3) 谢谢,会这样做!

4) 没有这个端口只是输出、我实际上是在尝试将它限制为 500mA 输出。 这反映在提供 5V 电压的限流器中。

5) 我认为 CM5 根本不需要该引脚、它没有 DIR 连接器、因为它本身不支持翻转、仅支持 USB-A 3.0 端口、因此我使用了该多路复用器。 我有点困惑、因为我认为多路复用器会自动处理端口的方向和翻转?

6) 同样、我认为 CM5 对此引脚或输入没有任何要求

7) 感谢将看!

我将很快发送标注的路线图像

您好、

感谢更新:

2) 我不确定您究竟是什么错误。 多路复用器的 CC 线路只能连接到单个 USB-C 端口、另一个端口具有 5.1k 电阻器、与此设计或原理图无关、它只是器件上的标记、但根本没有电气连接。[/报价]没有、我假设标记相同的布线已连接。 这通常是原理图设计的标准。 将来我建议使用不同名称的未连接网络。

[引述 userid=“646051" url="“ url="~“~/support/power-management-group/power-management/f/power-management-forum/1563570/hd3ss3220-schematic-and-layout-review-request/60256904) 没有这个端口只是输出、我实际上是在尝试将它限制为 500mA 输出。 这反映在提供 5V 电压的限流器中。

[/报价]当前使用 4.7k 电阻将电流模式引脚上拉至 3.3V。 我建议下拉此引脚、将广播从 3A 限制为 900mA、从而减轻限流器件的应力。

I 将 CURRENT_MODE 连接至 GND 以实现最低 900mA 限制、也将 ID 保留为悬空状态、因为不会使用它。 数据表提到 DIR 引脚需要 200k 电阻器连接到 3.3V 才能使器件正常运行、因此我保持原样。完美!

关于布局:

在大多数情况下、差分布线看起来都可以。 最好在每个高速布线下方/上方有一个实心接地平面、以正确耦合到地。 对我来说、路由本身看起来正常。

[/quote]