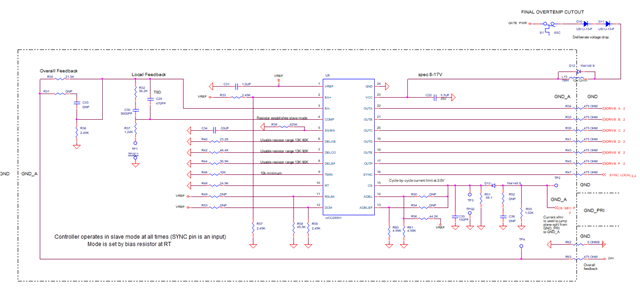

Thread 中讨论的其他器件:UCC28951、 UCC28950、UCC28950EVM-442

工具/软件:

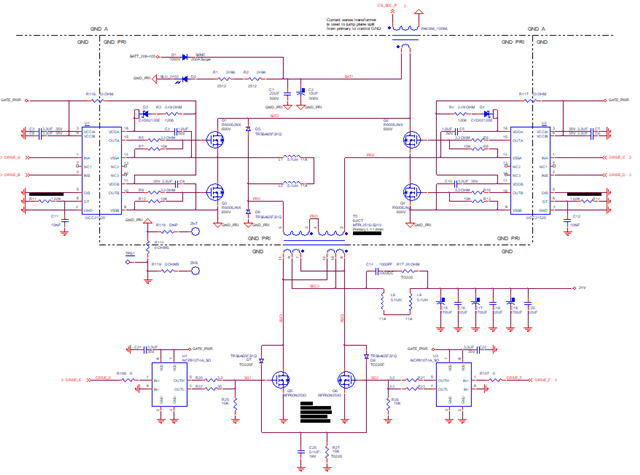

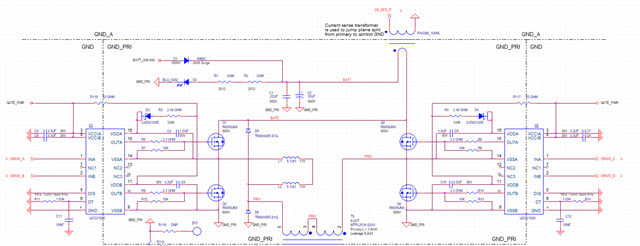

由于怀疑次级 FET 栅极连接或时序不正确而导致出现过功率反射次级电流斜坡的大电 流浪涌、我已检查了所有栅极驱动器的连接(我相信它们是可以的)、并使用 SLUC222D 重新计算 DELAB、DELCD 和 DELEF 的电阻。 在 CS-feedback 侧、我通过 4.99K 将 ADELEF 接地、 并将 ADEL 连接相同、但 44.2K 也连接到 VREF。 在调试这种破坏性电流时、我正在 25%的负载和相对较低的输入电源电压下运行、以避免电流调节。 (在全功率下,桥式 FET 只能持续几秒钟。)

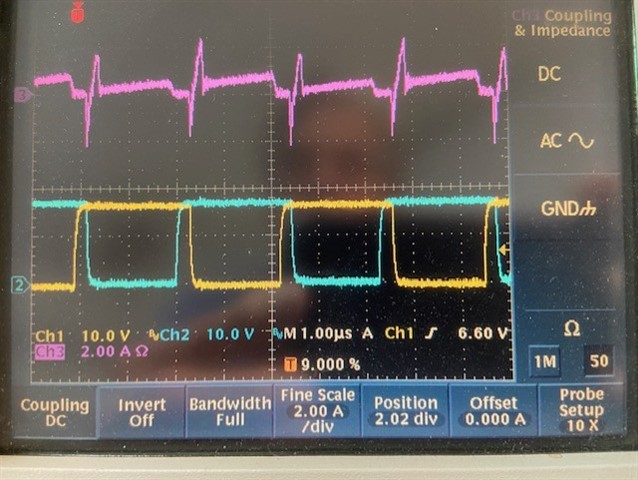

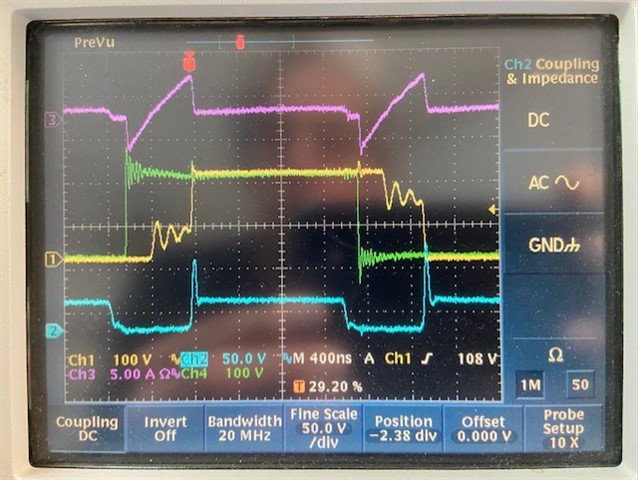

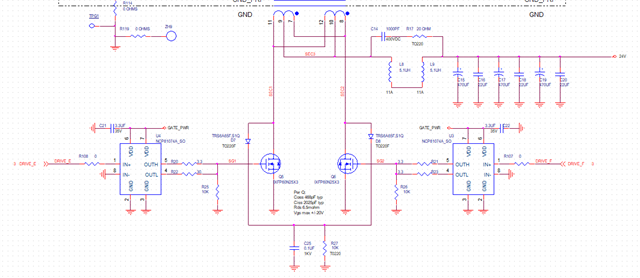

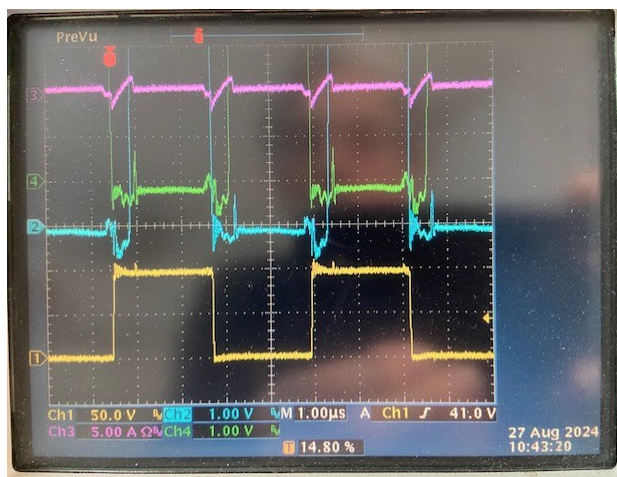

我在之前的帖子中发送的照片有一个误导性的迹线(品红色,从顶部第二个)、我错误地将它标识为次要的中心抽头、这是不可能的。 但至少它是一个邀请,以绘制辅助中心抽头应该是什么样的样子。 以下所有照片均来自上述经过延迟调整的电路。 第一张图片只有两条迹线:上面的迹线是电源输入电流、该电流是使用电流探头在电桥顶部测得的。 它仍会显示意外的浪涌以及预期的反射 — 次级电流斜坡。 较低的迹线实际上是次级中心抽头。 请注意、意外浪涌会消耗次级功率脉冲之间大约一半的死区时间、并在功率脉冲开始时精确结束。

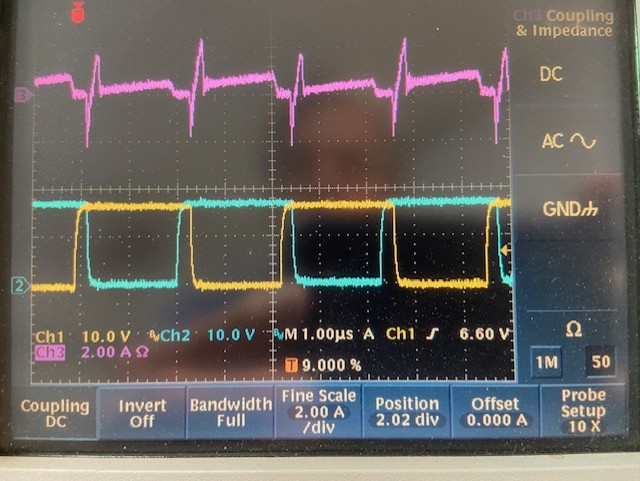

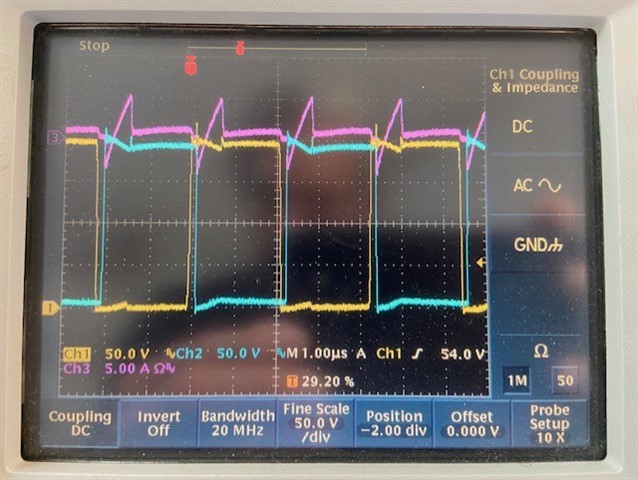

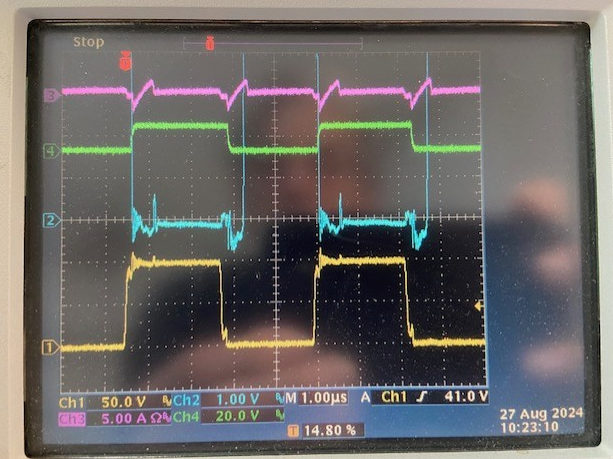

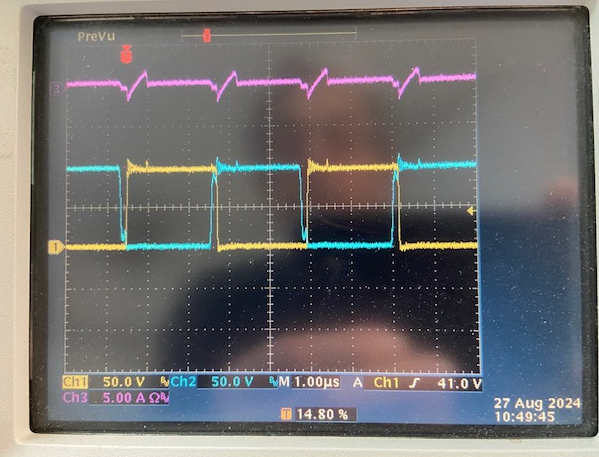

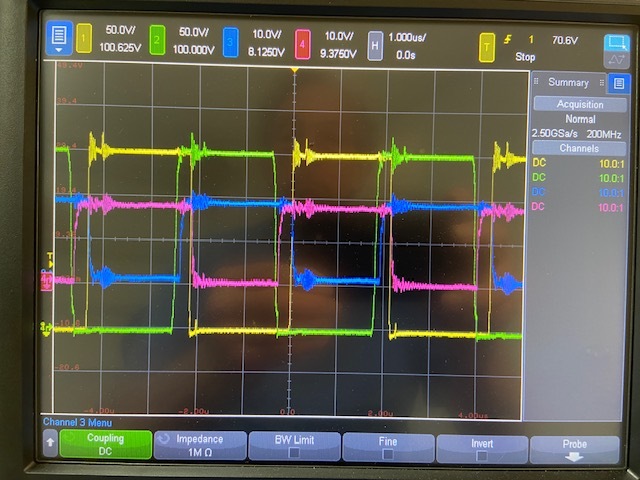

以下图片显示了桥的两端(黄色和绿色,较大的波形)以及两个辅助门(蓝色和品红色,较小的波形)。 请注意、栅极信号重叠其相应的初级信号时间、并且几乎彼此重叠。 这个时序是否正确?

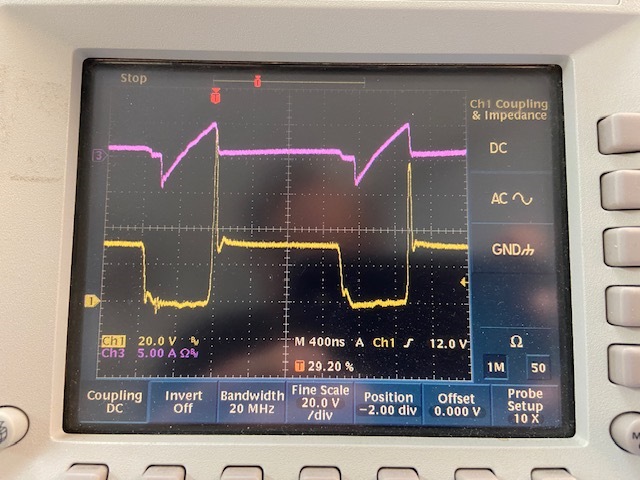

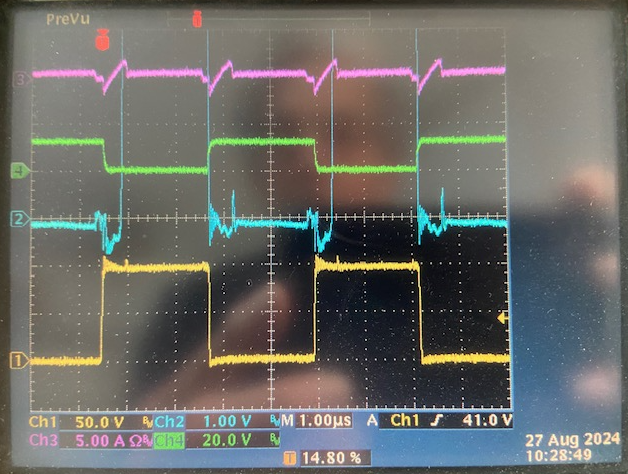

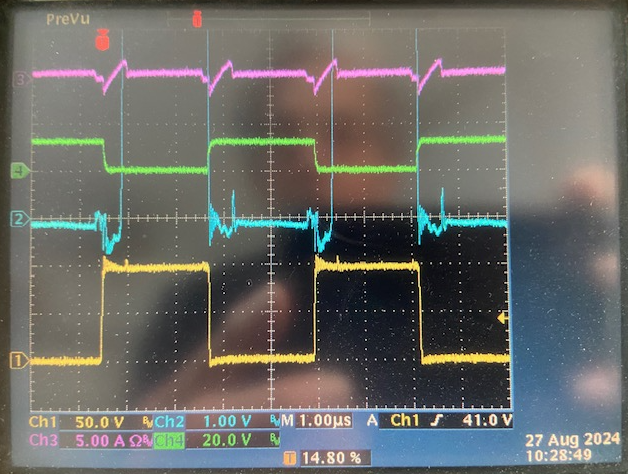

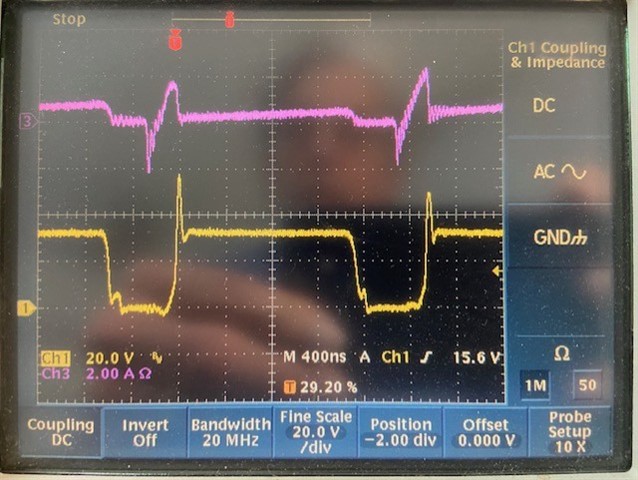

最后一张照片显示了初级电流和次级栅极。 在这里、看起来两个次级栅极确实重叠了。 请注意电流浪涌和明显重叠的栅极信号之间的对齐情况。 这些之间是否存在超越巧合的关系? 我很惊讶地发现这种重叠。 我使用的是 NCP81074A 栅极驱动器。 这些控制器具有单独的上升和下降输出。 现在、栅极电阻器相同且非常小(3.3 欧姆)。 我是否应该使上升电阻大大增大、以便尝试在次级 FET 导通时间之间实现某种程度的分离?