主题中讨论的其他器件:UCC24612、 PMP22806

工具/软件:

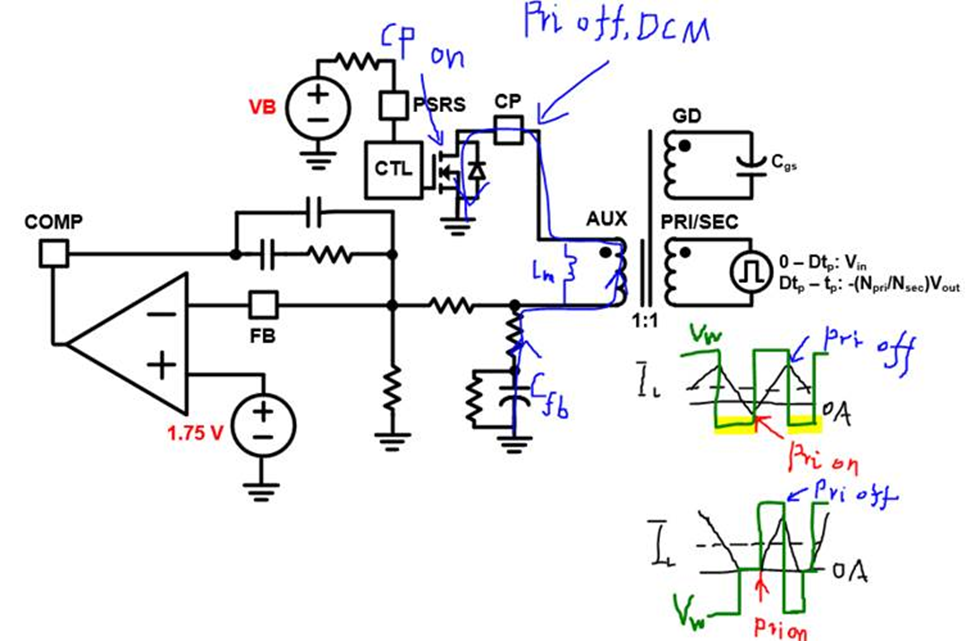

我担心 CP/PSRS 内部电路明显有缺陷。 带有 UCC24612 的 TPS23731 的第二个原型电路(另请参阅 e2e.ti.com/.../using-psr-control-using-aux-winding-and-synchronous-rectification-seems-to-suffer-of-increasing-output-voltage-on-low-loads) 在 PSRS 到 RTN 之间提供一个 0 欧姆电阻器、以便在无需额外绕组的情况下提供与使用次级整流器相关的更多测试选项(请参阅链接)。

在两种情况下、在尝试非全 CCM 模式后移除 0 欧姆电阻器后、应测量 8Ω 的电阻、然后在第二个电路板 3.5Ω 中重新测量。 这真的很烦人,也考虑到这里报告的问题: https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1211700/tps23731-cp-pin-damaged-on-long-duration-test。

查看数据表后、我看到 CP 上的电压可能不低于–0.3V(绝对最大额定值)。 这意味着:即使在与 tps23731EVM 相关的情况下、在 CP-MOSFET 关断之前非常短的负电压也可能会使内部电路老化、因为内部体二极管的正向电压约为 0.9V、当 PSRS 短接至 RTN 时更是如此! 因为在这种情况下、负电压将在整个主 MOSFET 关断状态时间内出现(或直至核心能量为零退磁)、数据表不会给出提示、例如在这种 PSRS 至 RTN 的情况下使用肖特基二极管。 实际上、在非全范围 CCM 模式的情况下、反馈环路中不需要肖特基二极管...因此、相关部分中的提示将会很有帮助(在第一个链接中提到的主题中,我还建议在本节中进行改进)。

幸运的是、我有第三个原型。 实际上、不焊接 TPS23731 并随后进行手工焊接是无法实现的。 现在、为了安全起见、我将在 CP 引脚上添加一个肖特基二极管。