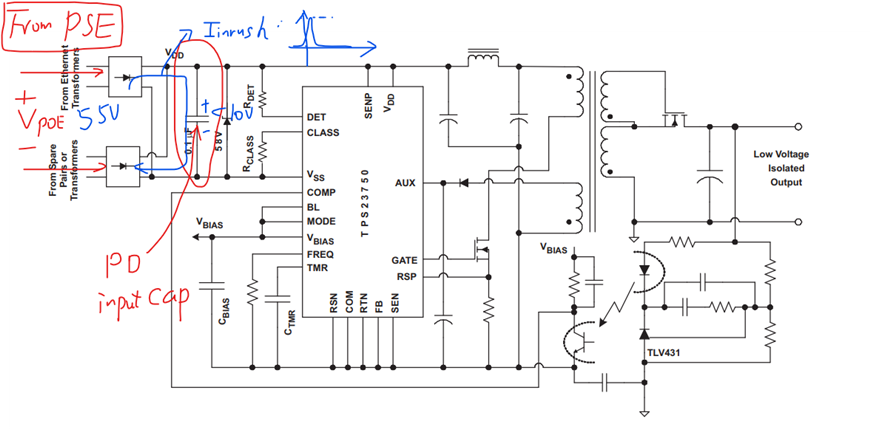

Other Parts Discussed in Thread: TPS23750

工具/软件:

大家好!

我对 TPS23750 有一个疑问。

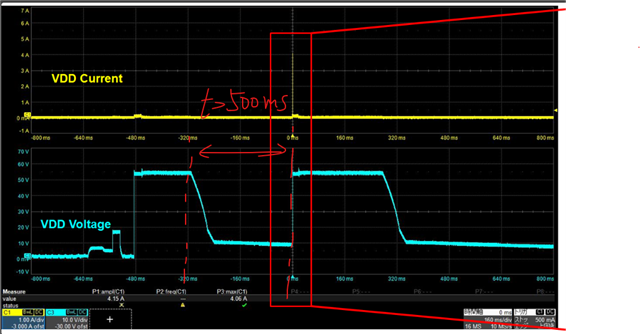

当 VDD 反复导通→OFF→ON 时、会产生约 4A 的浪涌电流。 我想确认是否可以防止这种情况、或者 TPS23750 是否按规定运行。

(1) 首先、让我确认浪涌限制的条件。 我知道、当 VRTN 超过 12V 时、将激活 140mA 浪涌限制功能。 这是正确的吗?

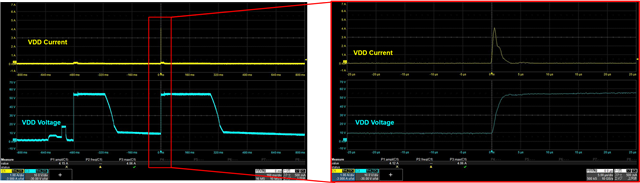

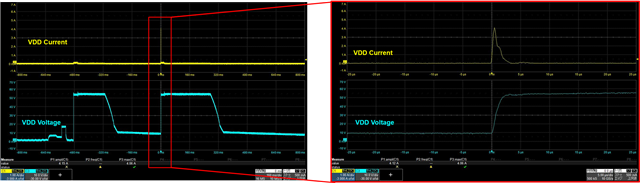

(2) VDD 重复开启→关闭→ON。 打开和关闭操作之间的时间间隔很短。

更具体地说、电源集线器协商提供 4%的电源、然后立即关闭。 之后导通时、会产生约 4A 的浪涌电流。

似乎在没有协商的情况下将其开启会阻止浪涌限制器激活、从而导致出现浪涌电流。

以下是 VDD 开/关和浪涌电流的波形。

浪涌限制未运行。 请说明这种现象是如何工作的。

此致、

Ishiwata