Other Parts Discussed in Thread: UCC29002, INA293, INA187

主题中讨论的其他器件: INA293、 INA187

工具/软件:

您好、Ulrich、

关于我之前的问题、现在已锁定、我们终于有时间对我们的系统进行更多测试、在进行更详细的测试时、我们注意到一些我们认为可能不寻常的事情。

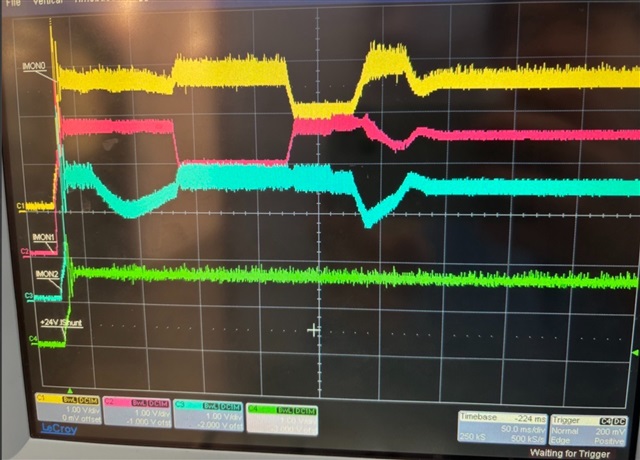

1) 每个通道的电流稳定到稳定状态所需的时间非常长,大于电压稳定时间的 50 倍。 电压在大约 7ms 内稳定、但无论电流阶跃变化大小如何、各个通道的电流都会在大约 350ms 后稳定下来。

2) 电流共享稳定在我们认为可能是一种不寻常的方式。 在初始部分看起来像欠阻尼振荡(大约前 10ms 左右)之后、在电流达到稳定状态之前、它看起来更像某种分段函数。

3) 所有这些行为都是在 2、3 和 4 个电源启用时看到的

4) 我应该注意的是、我们在分流电阻器和 CS+输入之间使用带有 INA293A2IDBVR 的低侧分流器、以改善对超过 UCC29002 数据表中规定的–0.3V 负输入的处理。

随附的图显示了 4 条 CSO 线路中的 3 条(图中的 IMON0-2)、第 4 条迹线是电子负载之前的高侧分流器(全部 4 个电源之和)。 虽然未显示、但电压在初始上升沿的 7ms 内稳定、第 4 条 CSO 线的行为与所示的类似。 请忽略 CSO 线路布线上可以看到的大量噪声、因为我们已经证明这是一个测量干扰

这是否都是预期行为? 此外、我们如何缩短达到稳定状态所需的响应时间? 我的担心是、在重负载条件下、电流不平衡的持续时间可能足够长、无法让我的其中一个电源触发过流保护。