工具/软件:

您好、

我的 TPS48161 应用遇到问题。 该应用的设计电压为 24V 标称电压 (18-32V) 和 30A 最大电流

我的应用需要启动容性负载、因此我使用软启动 MOSFET、并根据数据表将一些串联电阻连接到 G 并由 INP_G 控制。 主 MOSFET 连接到 GATE 并由 INP 控制。

当 I TEST 在空载条件下、INP 和 INP_G 输入分别驱动连接到 GATE 和 G 的 MOSFET 栅极、输出电压没有问题。

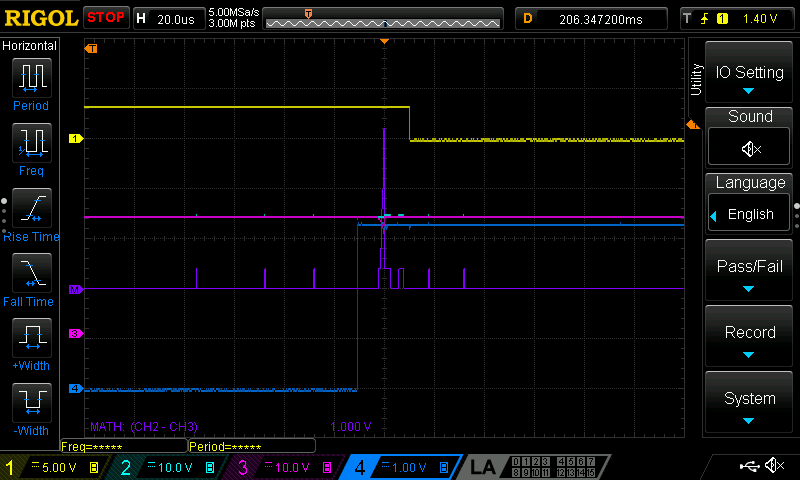

如果 I TEST 使用 100 Ω 负载、则将 INP_G 驱动为高电平会使 FLT 引脚置为有效(低电平)。 软启动 MOSFET 保持关闭状态。 当 INP_G 被驱动回时、FLT 置为无效(高电平)。 然后、连接到栅极的主 MOSFET 导通并升高输出电压。

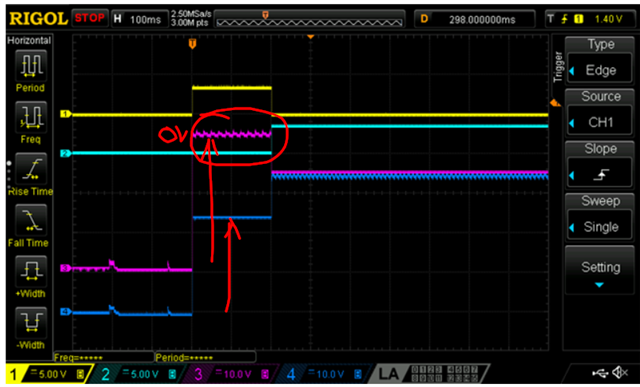

当 I TEST 使用 10uF 容性负载时、将 INP_G 驱动为高电平会导致 FLT 引脚置为有效(低电平)。 软启动 MOSFET 保持关闭状态。 当 INP_G 被驱动回时、FLT 置为无效(高电平)。 然后、连接到栅极的主 MOSFET 似乎导通、但似乎存在浪涌电流问题、并会很快关断。 输出电压很快上升到几伏、然后再次放电。

在如此小的负载下、为什么当 INP_G 被驱动为高电平时 FLT 会置为有效?

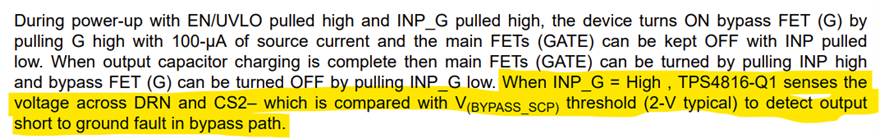

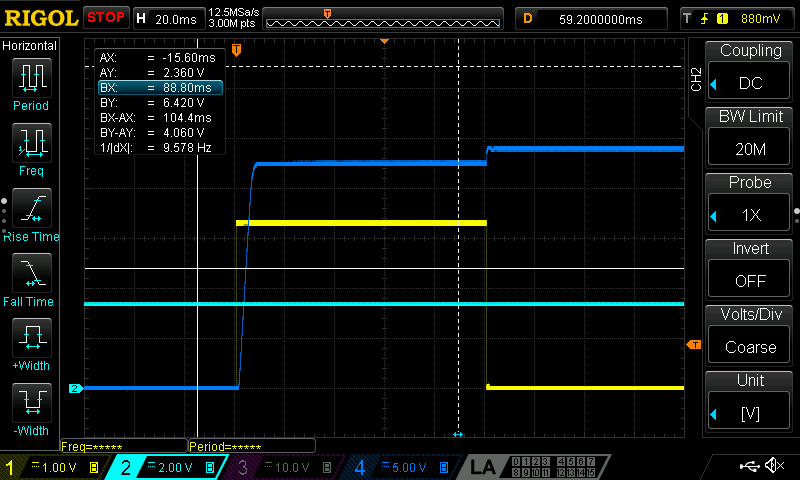

输入 1:INP_G、输入 2:INP、输入 3:G、输入 4:GATE

无负荷起动工作正常。 INP_G 处于高电平的相同序列持续 200ms、然后在下面的示波器捕获中重复 INP 处于高电平。

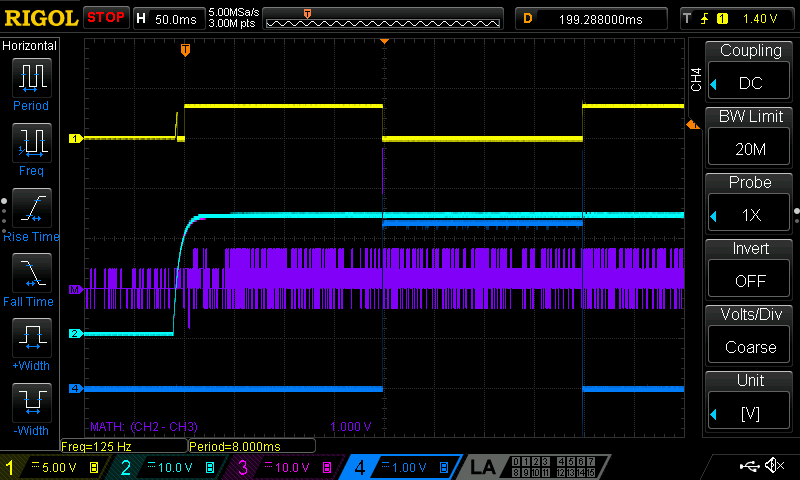

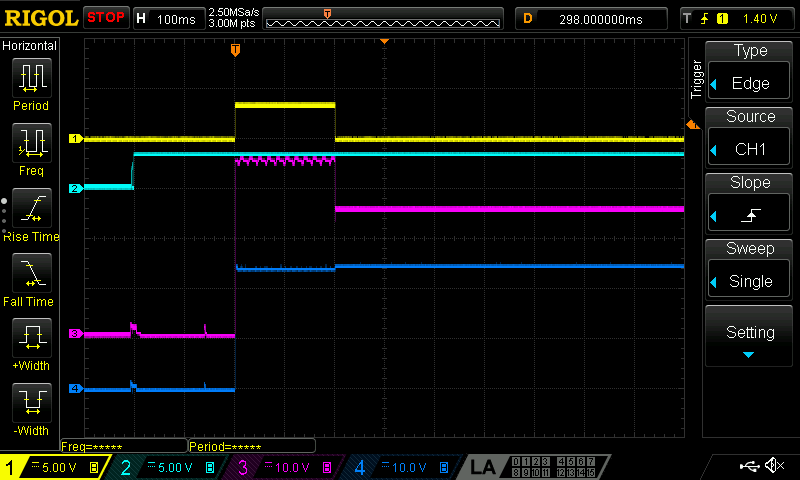

输入 1:INP_G、输入 2:FLT、输入 3:g、输入 4: 输出电压

无负荷起动工作正常。

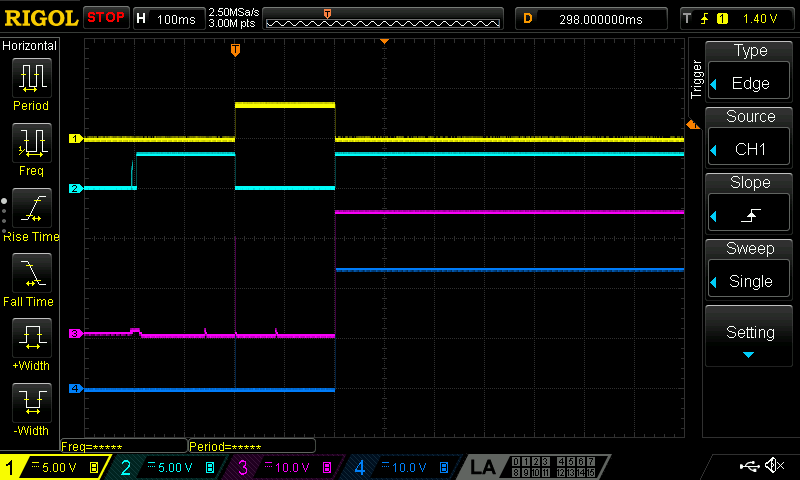

输入 1:INP_G、输入 2: FLT、输入 3:g、输入 4: 输出电压

100 Ω 电阻负载。 将 INP_G 驱动为高电平会使 FLT 置为有效(低电平)。 软启动 MOSFET 未导通。

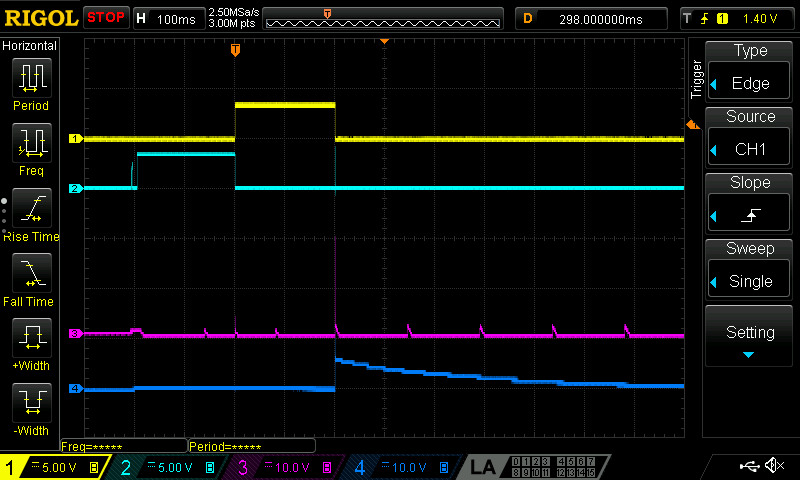

输入 1:INP_G、输入 2: FLT、输入 3:g、输入 4: 输出电压

10uF 容性负载。 将 INP_G 驱动为高电平会使 FLT 置为有效(低电平)。 软启动 MOSFET 未导通。 主 MOSFET 开启但关断速度非常快、导致输出电容器电压快速增加、然后再次放电。