主题中讨论的其他器件:TPS65224、 AM62A7

工具/软件:

您好、工程师

当我们使用 TPS65224 的 GPIO5 来执行 ADC 采集时、我们发现芯片的 ADC 采集端口默认情况下会自动启用下拉电阻器。 这导致在采集电压时 ADC 分压值逐步降低。 此外、收集的电压越高、压降越大。 我们尝试修改 GPIO5 寄存器的位 3 以禁用上拉电阻器、但它没有影响。 仅当将 GPIO5 位 6 和 5 设置为 GPIO 模式时、该功能才起作用。

您能告诉我是否有其他方法可以关闭此下拉菜单吗?

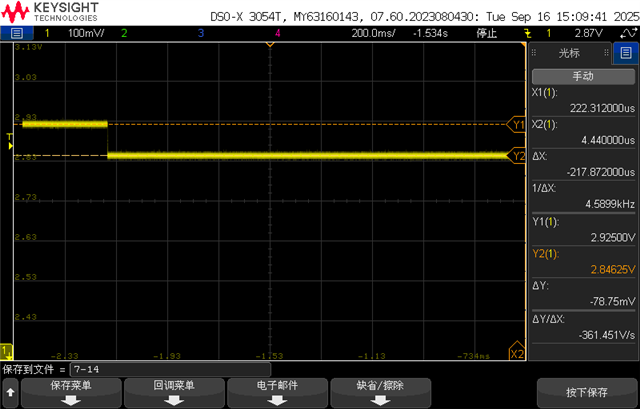

下图显示了启用 AD 采集后 ADC 分压器值的变化。

此时、我收集的电压为 32.5V、电压除以 100K 和 10K 电阻。

谢谢、

Xiwen