您好、我想寻求帮助来验证我设计的电路(FPGA 的核心电源)。 可以在 Excel 电子表格中看到限制条件(请参阅图像)。

1) 我对镇流电阻器和电压调节电阻器使用了 1%的容差。 这是可以的、还是值得寻找 0.1%的元件? (实际上,我使用电子表格进行了一些测试,似乎没有太大的不同,但我希望您的意见)。

2) Excel 电子表格推荐的最佳镇流电阻器看起来相当大,会产生压降。 是否需要对 LDO 电压进行补偿? 例如、将输出调节至 1.05V?

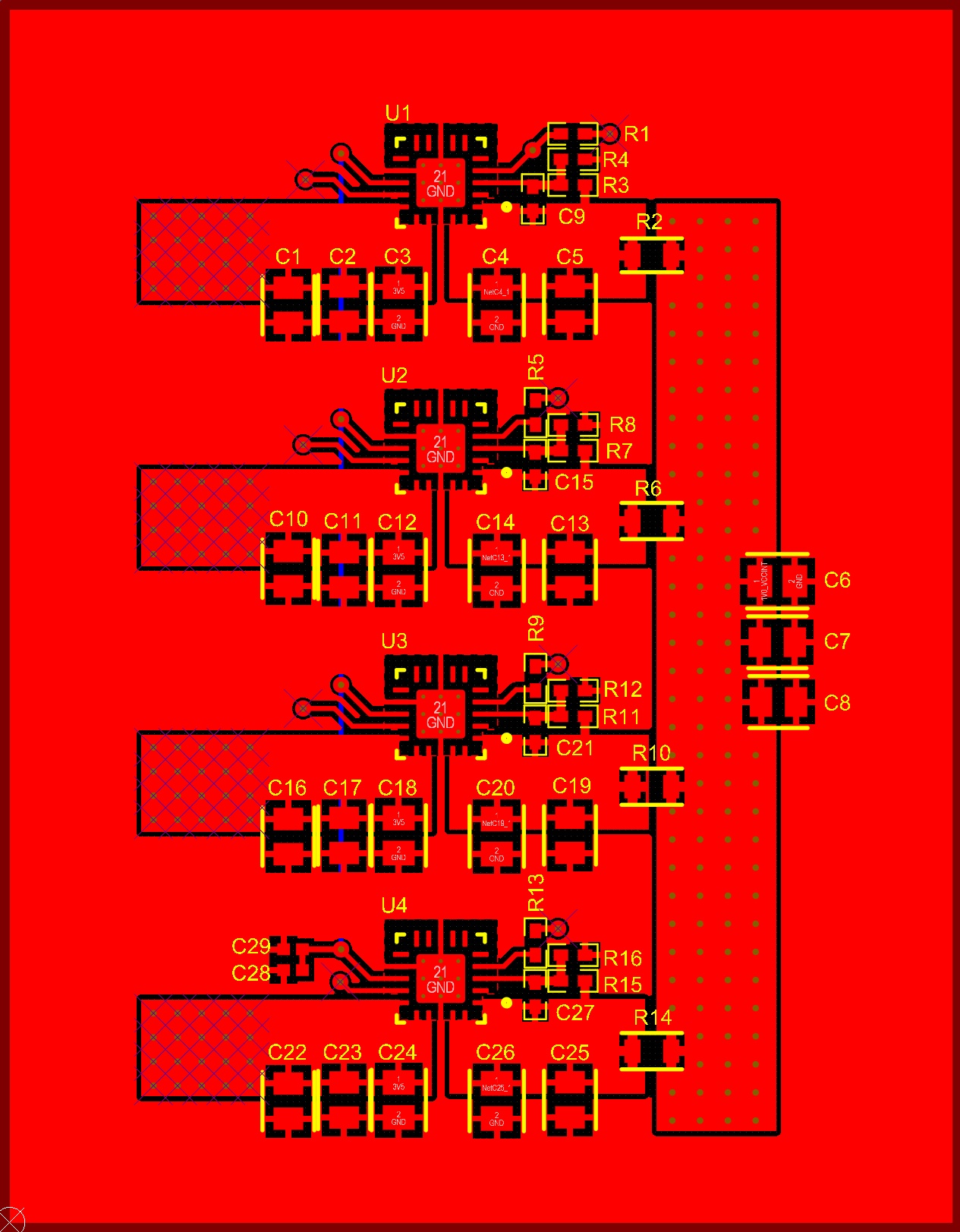

3) 物理布局是否正常? 在 LDO 输出部分、我决定避免使用电阻随温度变化的引线、并仅使用镇流电阻器进行连接。 你怎么看?

谢谢、大家好