Thread 中讨论的其他器件: UCC27201

工具/软件:

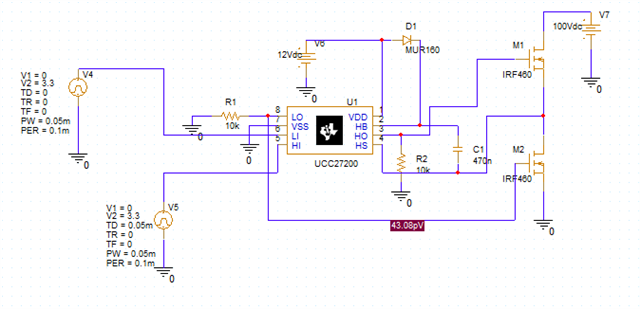

根据规格表、有两个 IRF460 错误。 我不知道原因、请告知。 谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Tom、

有时、将上升时间 (Tr) 和下降时间 (Tf) 设置为非常快的值会产生收敛误差。 我在 PSpice 中重新创建了您的原理图、当 HI 和 LI 的上升和下降时间非常短时、似乎就会发生这种情况。 我看到您的设置为 0ns、这可能会导致收敛问题。 我的原理图在 TR 和 tf = 10ns 时有效、这是一个实际的上升时间。

如果这样可以解决问题、请告知我们。

此致、

Amy

您好、Tom、

抱歉、以前没有看到这种情况、您的输入电压电平 (HI 和 LI) 过低。 UCC27200 是一款 CMOS 输入兼容器件、当输入引脚上的电压高于 6V(典型值)时、此器件会识别为逻辑高电平。 UCC27201 是一款类似器件、具有 TTL 兼容逻辑电平。 如果需要 3.3V 的输入电压、建议在设计中使用 UCC27201 器件。

请参阅下面来自 UCC2720x 数据表的:

此致、

Amy

您好、Tom、

1.您看到的压降有多大? 在相同设置下的仿真中、我看到大约 0.5V 的压降。 我测量了 12V 和 17V 之间的压降差、并且压降大致相同。 只要 HB-HS 的电压保持在 UVLO 以上、HO 就会继续正常开关。 如果 HB-HS 压降是一个问题、则自举电容器的大小可能会略微过大。 这里有一些需要权衡的地方、因为较大的电容器在启动时需要更长的时间才能充电。 此外、大电容器在高开关频率下也不能正常工作、而小电容器则不能正常工作。 请记住、旁路电容器 (VDD - VSS) 需要至少为自举电容的 10 倍。 我建议查看 针对半桥配置的自举电路选择 、以了解有关元件尺寸的更多信息。

2.为了与 HI/LI = 3.3V-0V 兼容、我建议 UCC27201。

如果您在 PSpice for TI 中需要额外的支持、或需要元件选型、敬请告知我们。

此致、

Amy

自举电容器 4.7uF 向 Cgs 放电以将其充满电、导致 M1 导通。 假设 Cgs = 3nF、4.7uF 电容器应非常快速地为 3nF 充电、因此 4.7uF 两端的电压应该几乎下降。 但是、为什么要对电压幅度进行如此显著的降低进行仿真呢? 此外、当我模拟超过 0.5V 的 12V 电源而在 17V 时几乎保持不变时、为什么电压会显著降低。 这与您的仿真结果不同、为什么?

此外、我在网上找到了带后缀的 IR2110 型号。 lib。 是否有任何方法可以使用只能导入的 PSpice for TI。 OLB 库?

您好、Tom、

1.为了正常工作、HO 引脚的下拉电阻需要在 FET 的栅极和源极之间连接。 栅极将根据 FET 的栅极和源极之间的差值开启。 因此、下拉电阻应位于 HO 和悬空接地端 HS 之间、而不是从 HO 到 GND。 这也是导致 HO 导通时导通电压下降如此大的原因。 在我的仿真中、将 HO 上的下拉电阻连接到 GND(如您所示)会导致压降超过 1V。 将 HO 下拉电阻连接到 HS 可降低 HB-HS 压降、因为它会降低下拉导致的功率损耗。

此外、10k 是一个非常强的下拉电阻、这也可能导致 HB-HS 电源的压降。 在设计中、下拉电阻的值在很大程度上取决于应用。 请记住、当将较小值的电阻用作下拉电阻时、其消耗的电流将大于具有较大值的电阻。

我在屏幕截图中也看到您的仿真中的电容值实际上是 0.47µF、而不是 4.7µF。 您可以增大自举电容器的大小、以进一步降低 HB-HS 电压、注意我在上述响应中描述的权衡因素。

2.请观看以下视频、了解如何将第三方模型导入 PSpice for TI:PSpice for TI:第三方模型导入

此致、

Amy

e2e.ti.com/.../ir2110_2D00_pspice_2D00_simulationmodels_2D00_en.zipI画错了、应该在 HO 和 HS 之间连接电阻器。

现在、移除两个下拉电阻器并进行仿真、将自举电容器更改为 4.7uF。 当电源电压为 12V 时、仿真结果显示骤降值为 11.4-11.2=0.2V。 假设 Cgs = 3nF、4.7uF 应能非常快速地为 3nF 充电、因此骤降值应该非常小、但为什么仍然存在 0.2V 的压降?

提供 15V 或 17V 电源时、自举电容器上的电压不会降低、但比电源电压低 2.5V 以上。为什么?

此外、我正在使用的仿真软件版本是试用版本、 “tool- Generate part“显示为灰色。 您能帮助我将 IR2110 的 lib 文件转换成 OLB 文件吗? 谢谢!

您好、Tom、

我无法重现您看到的问题、您是否能够发送波形的屏幕截图和更新后的原理图? 移除下拉电阻并增加自举电容后、我会看到 HB-HS 电压出现非常小的压降、该压降远低于 0.2V。 此外、对于 15V 和 17V、HB-HS 电压、我可以看到近似于 VDD 上的电压、减去二极管的正向压降。

我建议使用 PSpice for TI、而不是软件的试用版本。 PSpice for TI 具有向软件添加其他器件的功能。

此致、

Amy

您好、Tom、

感谢您发送原理图。 这有助于我了解问题是什么。 我假设您已切换到 UCC27201 模型、该模型与原始模型中的 0V 至 3.3V 输入兼容。

之所以会出现此行为、是因为输入从 3.5V 切换至 6.5V。 首先、我们建议从 0V 输入电压(强高电平和低电平信号)切换 。

但是、在 PSpice 中出现问题的根本原因是 UCC27200 与 CMOS 逻辑兼容、因此设计采用 0 至 VDD 电平的输入电压值驱动。 因此、输入电压阈值被建模为 VDD 电源电压的函数。 在我们的一些旧器件中、这些器件与 CMOS 逻辑控制兼容、输入电压阈值遵循 VDD、或以 VDD 的百分比的形式发送阈值。 我不确定为什么 UCC27200 采用这种建模方式、因为尽管该器件设计为与 CMOS 逻辑配合使用、但这并不代表器件的实际行为。

无论如何、在 15V 或 17V 时未看到 HB-HS 电压 DOP 的原因是输入(从 3.5V 切换至 6.5V)未达到模型中的输入阈值。 因此、该模型的内部逻辑会将输出保持为低电平、这意味着电容器没有放电、所以 HB-HS 上没有压降、因为没有任何东西正在使电容器放电。 调试模型时、我始终建议在调试系统的其他部分之前探测输入逻辑和输出逻辑、以确保模型的逻辑正常运行。

我已将 UCC27200 添加到待更新的模型列表中、但这个过程可能会很长。 同时、我建议使用 UCC27201、因为它与 0V-3.3V 兼容。

您可以在以下位置下载 PSpice for TI: PSpicefor TI 设计和仿真工具

此致、

Amy