Other Parts Discussed in Thread: TPS1685

器件型号: TPS1685

尊敬的 TI 社区:

我使用 TPS1685 0 (自动重试型号)适用于 VIN = 27V、ILOAD 高达 10A 且 EN 线路由传感器从外部驱动的电子保险丝应用。

IC 正常工作,但我们经历了几次非常时髦的芯片行为:当负载被反复移除和恢复时,芯片可能进入一个奇怪的状态,无法激活开关,也无法恢复到正常状态。

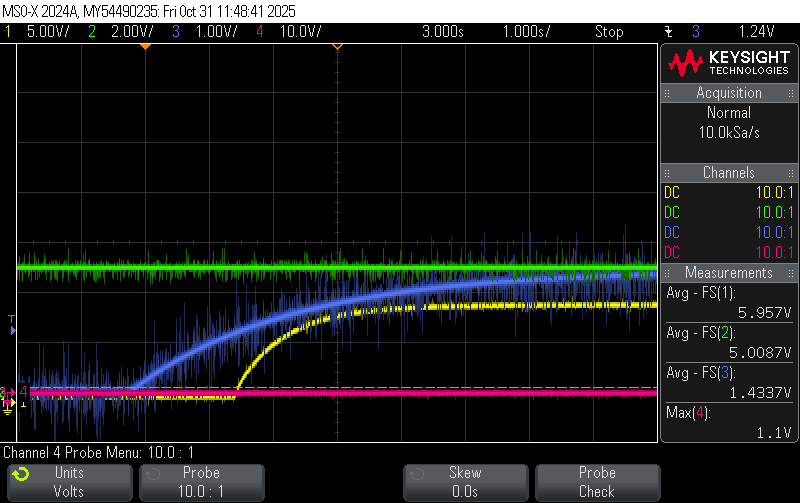

请查看以下范围:

-

蓝色 :EN -->从外部从低到高切换

-

黄色 :VOUT -->响应 EN 信号时、VOUT 从 0 增加到 9V(即使 VIN=27V)

- 绿色 : flt/-->始终为高电平:未触发故障;我还仔细检查了表 7.4 中的任何一个条件是否实际触发

-

红色 :PGOOD -->始终为低电平:电源不正常

- SWEN(上面未显示)-->始终为低电平(在我们的电路中保持悬空)

(您在上面的波形上看到的噪声主要是由于长示波导线;用短导线进行示波时几乎消失)

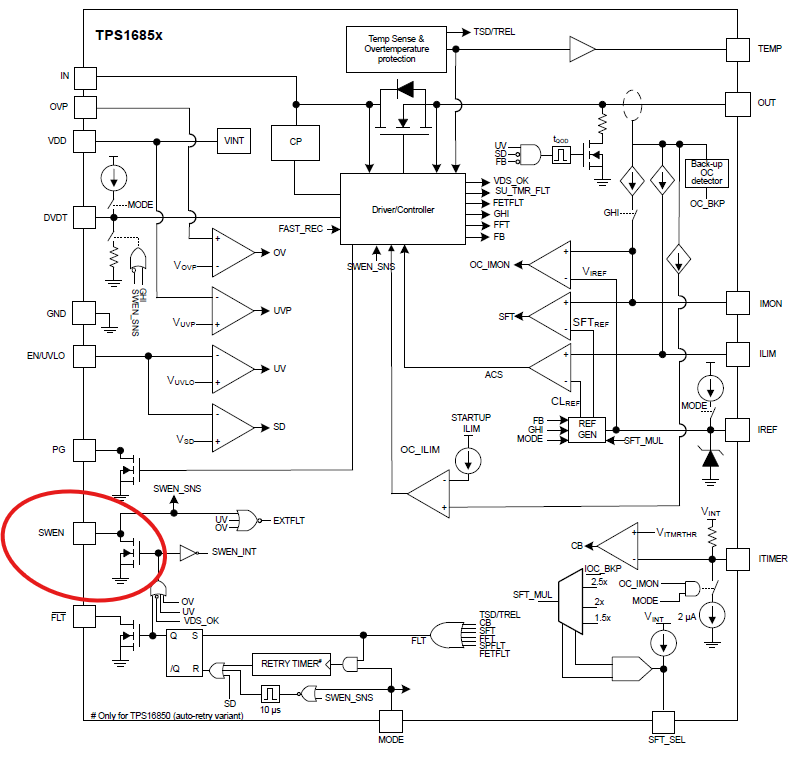

我还尝试在 SWEN 线路上添加一个连接至 5V 的 1k 上拉电阻、仍然被阻止至 0V、证明该上拉电阻被芯片在内部拉至低电平。

进入这种情况时、在我复位 VDD 引脚对芯片进行下电上电之前、我无法恢复正常运行。

在这种情况下、我有几个问题可以更好地了解发生了什么:

- 您是否知道任何可能触发这种不必要的锁存状态的特定条件? (请注意,我使用的是具有自动重试功能的 TPS16850)

- 即使 VIN 为 27V、VOUT 也会被钳位到 9V 是否有原因?

- 在我们的正常用例中、我们无法复位 VDD 引脚;那么还有其他方法可以恢复芯片的正常状态吗?

欢迎您提出任何建议或建议。

谢谢、