“线程: 测试”中讨论的其它部件

[2022年1月1日更新,软件的低阻抗是由超电容的低阻引起的。 我将进一步调查并更新此帖子-请现在不要回复此帖子!]

大家好,

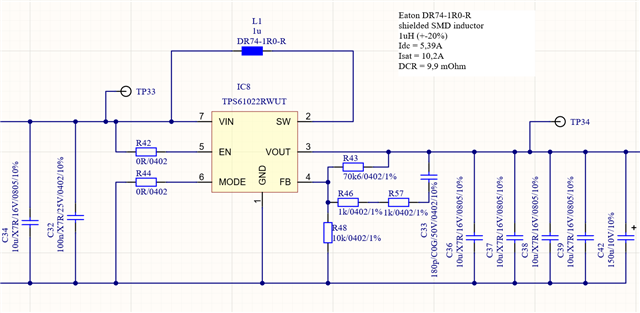

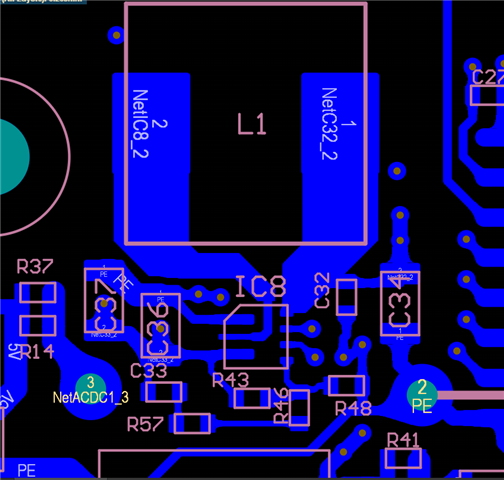

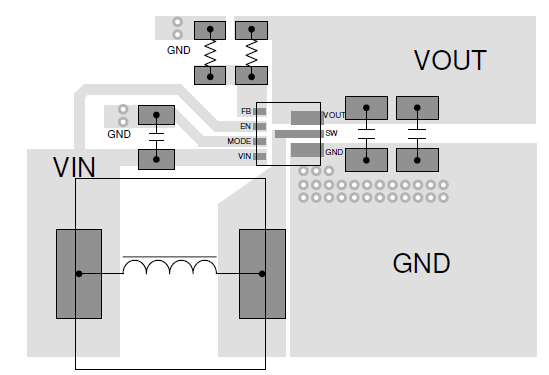

我正在将 TPS61022用于超缓冲电源应用。

我们的其中一个机组运行良好,而且上盖的设计电压为2.36V,持续放电至约0.5V。 当我测量开关到 GND 的电阻时,电阻非常高(>1 Mohm)。

在其他4个装置上,我测量的开关到接地之间的电阻约为0.5欧姆。 其中两项测试显示,上盖的电压仅为0.15V 左右。 我想知道 TPS61022是否因布局问题(例如,高 SW 节点振铃)而损坏(如其他帖子中所述)

但是,另两台设备从未使用输入电压进行过测试,如果我们知道物理定律在我们一侧,则也应该不会损坏(但这些设备也显示从 SW 到 GND 的低阻抗!)。

我想知道这3个案例中的哪一个是正确的:

- 使用万用表测量时,默认情况下,开关引脚对地的阻抗应该或可以很低

- 切屑下方的开关接地短路时存在焊接问题

- TPS61022损坏

如果案例1为真,您能告诉我吗? 我会尝试去除一个无法正常工作的装置上的一个芯片。

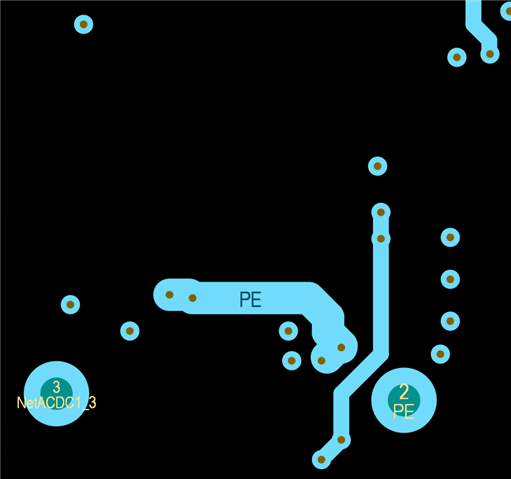

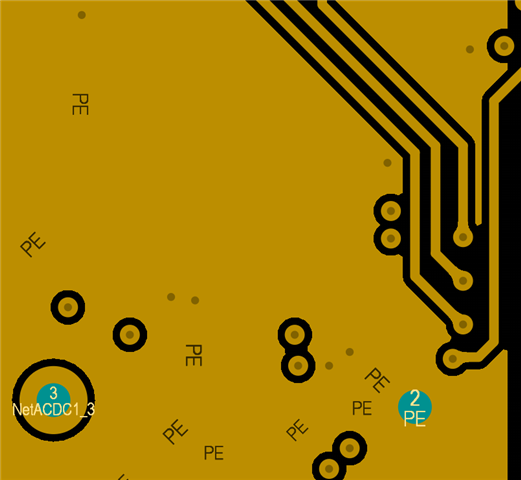

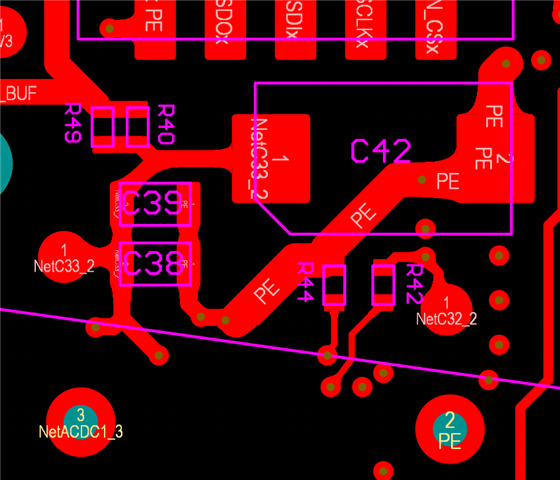

我会附上一张赛道图片。 BTW:输出连接到5V 适配器输入导轨。

谢谢!