“线程:测试”中讨论的其它部件

大家好,团队

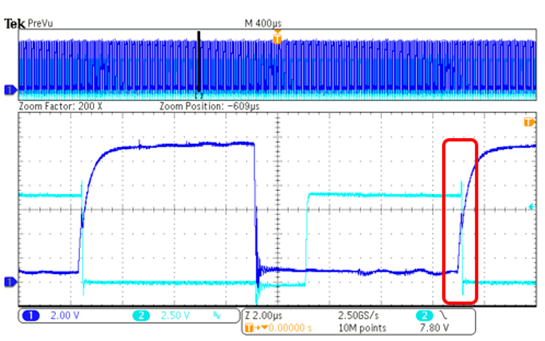

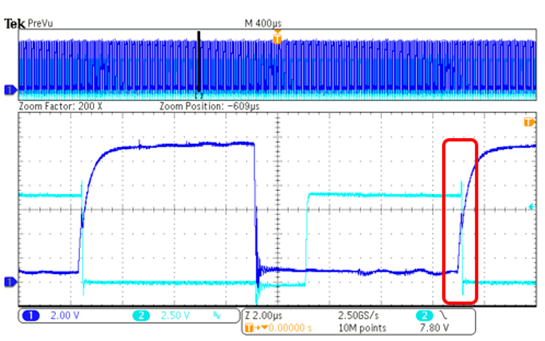

我的客户使用 UCC24612-2在 PFC 电路中进行 SR MOSFET 控制,他发现 CCM 下有一段很短的 VGS 超支期,如下图所示。

这是否会对高/低侧 MOSFET 造成直通风险? 在 SR FET 关闭和主 MOSFET 打开之间增加一些死机时间是否有问题?

CH1:PFC 主 MOSFET VGS

CH2:SR MOSFET VGS

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好,团队

我的客户使用 UCC24612-2在 PFC 电路中进行 SR MOSFET 控制,他发现 CCM 下有一段很短的 VGS 超支期,如下图所示。

这是否会对高/低侧 MOSFET 造成直通风险? 在 SR FET 关闭和主 MOSFET 打开之间增加一些死机时间是否有问题?

CH1:PFC 主 MOSFET VGS

CH2:SR MOSFET VGS

嗨,查尔斯:

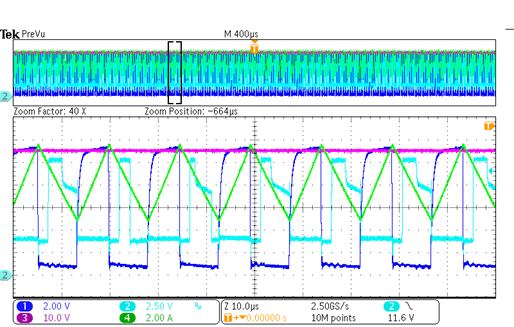

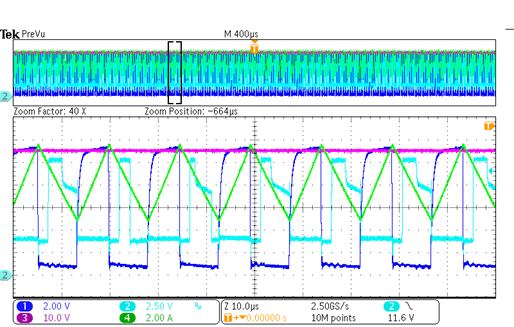

VDS 电压为100V。 我认为这是一种动力,而不是 PFC。 我是对的吗?

在 CCM 同步增压拓扑中,需要先打开低压端 MOSFET,然后更改高压端 VDS 极性。 因此,浇口必须在短时间内重叠。 根据您所分享的波形,IDS 不显示直通现象,波形正常。 但是,VG 的持续时间在这里并不稳定。 这意味着虚拟磁盘有噪音可以提前关闭 VG。 它可能会导致更高的传导损耗。 它可以通过布局来改进,以通过杂散电感来减少影响。

客户用作高/低侧的 MOSFET 是什么? 为了减少高端 MOSFET 的放电路径的 RG 和增加低端 MOSFET 的充电路径 RG,这是一种使这种情况更安全的方法。

此致,

韦斯利