“线程”中讨论的其它部件:LM94022, INA240, 测试, TPS737

您好,论坛

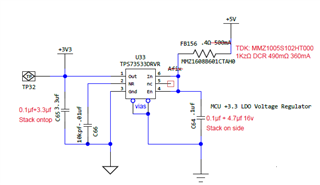

我的系统具有2个73533 LDO 稳压器输入+5V04。 一个 LDO 具有+3v307隔离输出,可为多个独立的 TI 器件供电。 另一 个电源 MCU (105°C 温度范围) VDD 导轨的最小电流为+2v97,因此存在极差的 EMI 抑制,很容易导致 MCU 崩溃。

替换 LDO (+2v97)没有任何区别,输出至无源4k8Ω Ω 轨负载,LDO 勉强过热而不是过热。 不同 TI MCU 的印刷电路板布局不同(相同的85°C 类),可将+3v309保持为无源4K3Ω VDD 导轨负载。 两个印刷电路板都具有相同的+5V04 150MHz bucking 稳压器,通过1KzΩ Ω,490mΩ Ω DCR 350mA 铁氧体,在输入引脚6处具有4.7uf+100nF (并行)。 1kzΩ 铁氧体阻抗与 LDO 输出(2v970)没有任何区别,因此现在仍保持较高的 µ A。 LDO 数字接地引脚平面是通过 FB1 (0Ω Ω<50mohm)电阻器与较大的降压调节器模拟接地平面隔离的部分平面,以进一步降低+3V3导轨对 MCU 的电磁干扰。

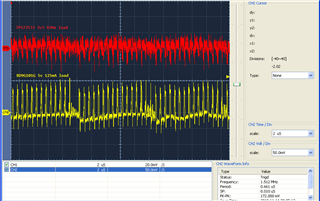

然而,温度较高的 MCU 级(105°C) VDD 导轨(4K8Ω)似乎将 LDO 输出向下拉至+2v97,从而导致 PSRR 异常和 EMI 抑制不良。 LDO 输出具有3.3µF +100nF (并行)-即使用4.7µF 替换,也没有任何变化,输出在 MCU 的 EMI 危险区仍为+2v97。

如何查找具有+2v97输出异常的 LDO 的原因?