“线程: TPS65086”中讨论的其它部件

您好,

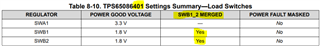

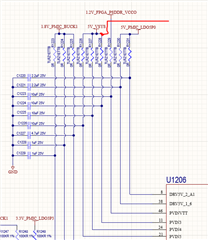

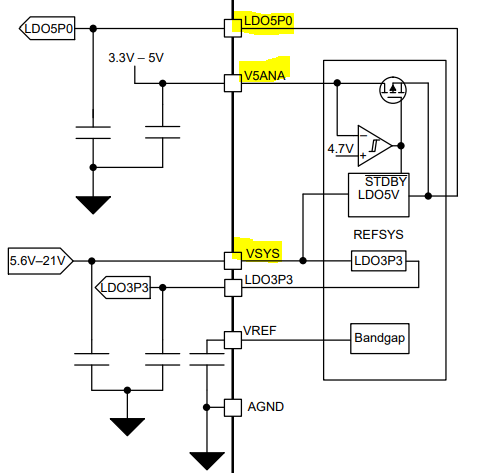

我使用的设备是 TPS65086401,用作 Xilinx Zynq UltraScale+ MPSoC 的 PMIC (MPN:XCZU3CG-1SFVC784E)

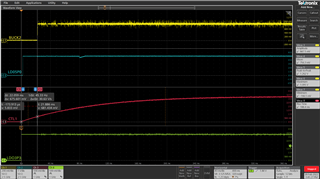

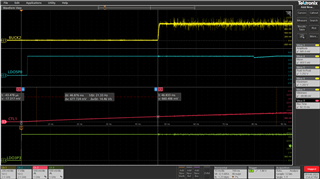

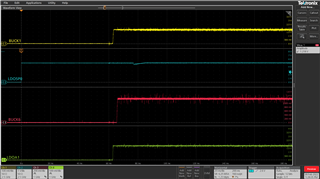

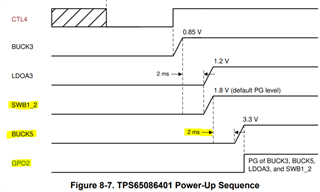

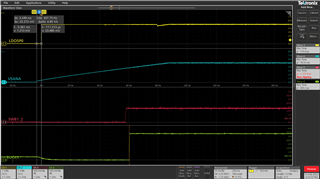

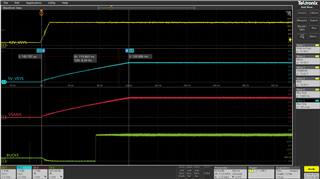

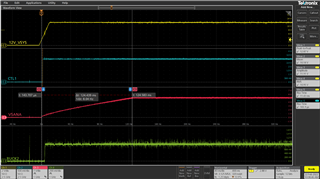

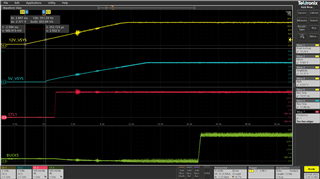

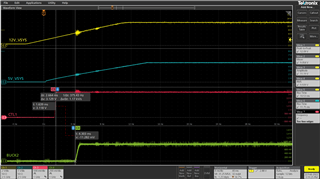

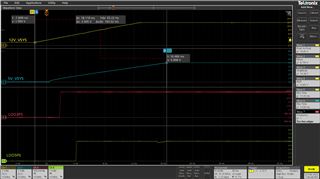

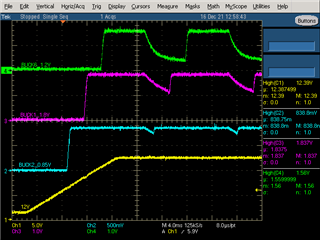

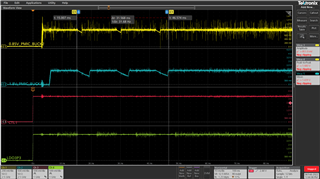

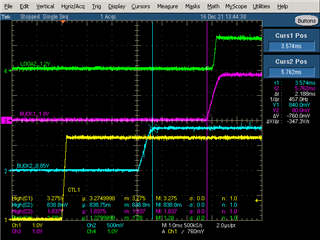

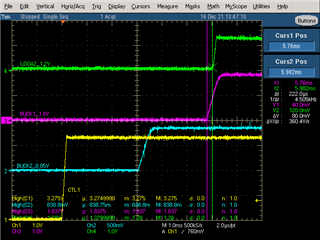

尽管我有电源和 FPGA 能够通电,但我观察到启动期间降压控制器的所有输出(Buck2,BUCK1和 BUCK6)都出现了骤降。

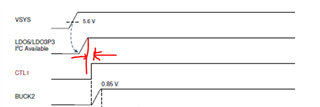

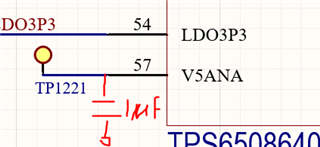

从我们的测量结果来看,vsys (我们的情况下为12V,上图中未显示),LDO3P3和 CTL1似乎是稳定的。 这些是 Buck2输出之前的电源/信号。

所有的下降都发生在对 seqeucne 的电力的初始阶段。 之后,它们是稳定的。

是否有任何可能的原因导致这种情况?