“线程”中讨论的其他部件:UC1844A,

您好,

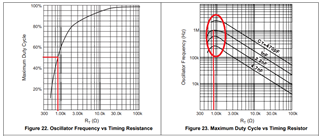

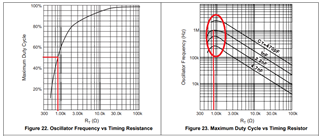

我计划以300kHz 切换频率 和最大工作周期%50来驱动我的 FET。 因此,我将尝试将内部振荡器设置为600kHz。

但是,当我根据数据表中的以下曲线对其进行排列时。 我看到我会在我的运营区域出现乐队的地方工作。

我担心在乐队周围工作。 温度效应和老化可能会影响我的烧切频率。

考虑到 IC 工作温度范围适用于长寿命设计,在这一点上工作是否安全?

振荡器频率是否有任何可能的牵引力,因为这是长期工作的频段?

请对我的担忧发表评论。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

我计划以300kHz 切换频率 和最大工作周期%50来驱动我的 FET。 因此,我将尝试将内部振荡器设置为600kHz。

但是,当我根据数据表中的以下曲线对其进行排列时。 我看到我会在我的运营区域出现乐队的地方工作。

我担心在乐队周围工作。 温度效应和老化可能会影响我的烧切频率。

考虑到 IC 工作温度范围适用于长寿命设计,在这一点上工作是否安全?

振荡器频率是否有任何可能的牵引力,因为这是长期工作的频段?

请对我的担忧发表评论。

您好,

感谢您的更正。 在初步设计阶段,最好能听到这个答案。

我在数据表中看到了一些关于不使用低于5Kohm 的 Rt 的线索。 但是,这方面没有直接的限制。

数据表图16和图17中的 Rt 应该大于5Kohm,这一点有一定的线索。

但是,我也无法理解死时间问题。 这是一个单驱动输出 IC,我认为不会出现死机问题。

1)请说明用户如何理解 Rt (作为正常操作的限制)应高于5Kohm?

2)请告诉您,为什么此 IC (UC1843A-SP)出现死机问题? 由于单个 PWM 输出,FET 的配置没有直通。

3)我不想限制自己使用 UC1843A-SP 的目的。 我认为,%0-%80占空比配置可以比%0-%50占空比性能更好。 请确认。

此致

您好,

1)如果 Rt 太小,表示 CT 大和充电电流大,则放电 CT 需要最短的死机时间,同时,残留 Rt 还在尝试为 Ct 充电。因此,过小的残留器将限制高频率。

2) 更大的 CT,更大的死时间和更小的 Rt.将导致问题,如1所述),TI 建议的死时间不要超过15%。

3) 我认为不是这样,最大工作周期由您的设计决定,并在正常工作负荷和最大工作负荷之间保留足够的工作边际。