部件号:UCC27624

是的,您可以并行使用双通道低端驱动器的通道,例如 TI 的新型 UCC27624。 这将通过与通道并联来提供几乎双倍的驱动强度。 如果您作为一名设计师希望避免并行两个驱动器通道的额外工作,以获得额外的驱动器强度,您还可以考虑 TI 新的单通道低端驱动器 UCC27614 ,它具有10A 源/汇电流。

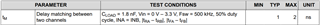

并行通道的首要考虑之一是查看栅极驱动器“两个通道之间的延迟匹配”规范。 延迟匹配指定信道之间的内部传播延迟的匹配程度。 换言之,如果信号同时应用于两个通道的输入,则两个通道输出的延迟时间差是延迟匹配规范。 与规格匹配的延迟越小,栅极驱动器的性能就越好。 以 UCC27624为例(请参阅下面的数据表规格表),我们看到典型延迟匹配为1ns,最大延迟匹配仅为2ns! 这将使设计师在将输出连接在一起时高枕无忧,因为这可以减少两个输出阶段的拍摄机会。 使用最大延迟匹配2 ns 通道的栅驱动器是一个很好的经验法则。

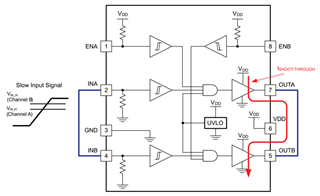

当直接将输出引脚和 OUTB 引脚连接在一起时,必须小心操作,因为在打开或关闭过程中,两个通道之间的任何延迟都可能导致直通电流传导,如下图所示。

µs 确保延迟匹配规格足够,使用快速上升时间为20 V/m Ω 或更高的输入信号也很重要。 这是因为两个通道之间的输入阈值电压水平可能存在微小差异,这可能导致两个输出之间的延迟,特别是在使用慢速 DV/dt 输入信号时。

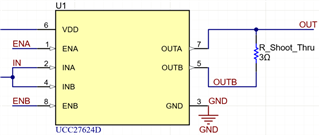

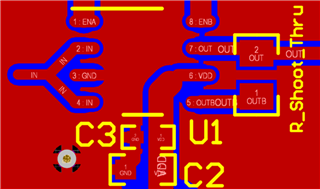

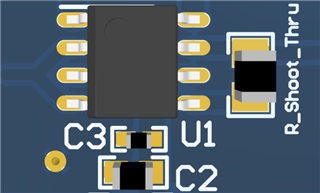

如果设计师希望更加安心,或者使用的驱动器的延迟匹配规格低于预期,请考虑在两个输出之间放置一个电阻器,如下图所示。 如果发生直通,“R_Shoot_Thru”电阻器将有助于限制直通电流。 设计人员通常在此处放置一个0Ω(短)占位符,以便在以后提供灵活性。

注: 虽然 UCC27624具有两个启用引脚的内部上拉电阻,因此可以浮动;TI 建议这些引脚直接短接到 VDD 引脚。 如果设计师想使用启用引脚,他们必须尽可能地将启用引脚连接在一起(就像输入引脚一样)。

---

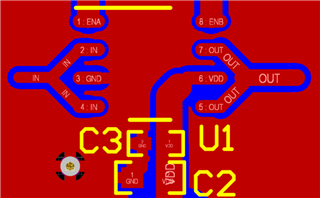

布局是并行驱动器通道的另一个非常重要的部分。 在创建 PCB 布局时,请考虑以下因素:

- 输入必须尽可能靠近设备连接(使用对称轨迹)

- 输出必须尽可能靠近设备连接(使用对称跟踪)

- 可选:两个通道输出之间的电阻器可帮助降低直通损坏的风险

请参阅下面的两个布局示例作为参考(这些示例使用 UCC27624D)。 第一个示例显示了一个布局,其中包含紧密相连的轨迹,这些轨迹在输入和输出引脚上都是对称的。 第二个显示相同,但具有直通限制电阻器。

电源培训小程序码