您好,TI支持团队:

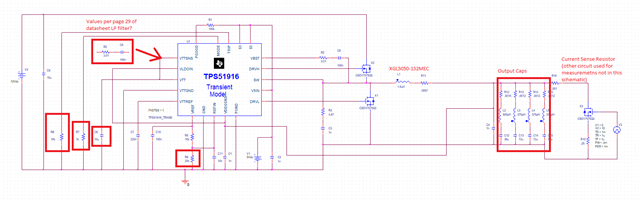

我正在DCAP-2模式下的DDR4应用(1.2V)中使用TPS5.1916万,具有跟踪放电-模式0 (在下图中的R7处使用1kOhm电阻器)。 将6.5A作为我的输出电流限值。

为DCAP-2模式选择R1和R2时,我是否应该使用数据表中的0 ESR公式6? 这让我的应用程序达到2万,与Webench相匹配。

RtTrip计算结果大约为12K,但PSpice中的模拟似乎表明10K将接近6.5A限制。 TI将采取什么行动? 在6.5A以上不应发生损坏,但我将开始碰到所选电感器的10 % 电感下降。 老实说,我甚至不会期望看到超过4.2A的电。

第29页的布局指南中提到的低通滤波器是否有目标角频率? 我确信 VTT输出电容的ESR (图中的C8)大于2mOhm。

TI在使用Coilcraft的XGL5050-152MEC电感器时是否会遇到问题,照片中显示的输出电容是否足够? 我使用Murata的模拟冲浪来获得输出电压降额和消瘦,以便更准确一点... 它们是一个47uF和3个100uF X5R保护罩。 广泛的温度范围不是主要问题。

谢谢!

Donald Weaver