主题中讨论的其他器件:UCC53X0S

混合上拉结构如何影响栅极驱动器?

电源培训小程序码

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

主题中讨论的其他器件:UCC53X0S

混合上拉结构如何影响栅极驱动器?

电源培训小程序码

栅极驱动器需要注意芯片内部耗散的功率、以保持温度范围。 这是内部芯片的一个因素、我们的一些栅极驱动器中的输出级具有混合上拉结构、可在米勒平坦区期间实现高效电流输送、从而为功率 MOSFET 或 IGBT 实现低开关损耗。 混合上拉输出 OUTH 包含一个与 N 沟道 MOSFET 并联的 P 沟道 MOSFET。 要了解混合上拉结构的有效电阻、我们需要了解 MOSFET 的基本工作模式条件。

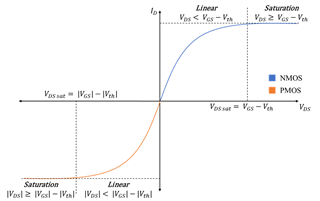

图1:NMOS 与 PMOS 运行模式

图1显示了 N 沟道、NMOS 和 P 沟道、PMOS、MOSFET 的 I-V 曲线。 以 NMOS 为例、I-V 曲线可显示三个区域。 当栅源电压 VGS 低于阈值电压 VTH 时、器 件将处于截止模式(VGS < VTH)。 在此区域中,设备将关闭,不会传导电流。

当漏源电压 Vds 小于 VGS 和 VTH 之间的差值时 、NMOS 将处于线性区域(Vds < VGS - VTH)。

当 VDS 大于 VGS 和 VTH 之间的差值时 、它将处于饱和模式(VDS > VGS - VTH)、其中 MOSFET 充当电流源并消耗最大功率。

NMOS 和 PMOS 之间的主要差异是栅极电压。 PMOS 由负电压驱动、NMOS 由正电压驱动、但这在栅极驱动器外部是不可见的。 栅极驱动器输出级的最简单版本是使用 PMOS 作为导通器件、使用上拉电阻器、使用 NMOS 作为关断器件、下拉电阻器。 PMOS 是上拉的最佳选择、因为当它完全导通时、当输出被钳位到电源轨时、没有二极管压降。 使用 NMOS 本身时、可能会出现压降、具体取决于栅极的控制方式、例如使用电荷泵电路。 但是、根据 PMOS 特性、在相同的额定电流条件下、其尺寸通常比 NMOS 大。 因此,TI 的许多栅极驱动器芯片中都使用了混合上拉结构,以提供较小尺寸的高输出电流。

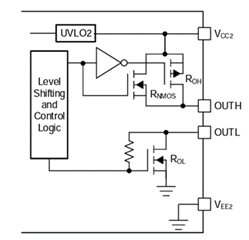

图2:输出级-- UCC53x0S

上图显示了分离输出栅极驱动器的输出级、这意味着导通引脚与关断引脚分离。 如前所述、使用混合上拉结构的栅极驱动器利用并联的 NMOS 和 PMOS 为快速导通提供高峰值电流。 借助下拉电阻器、可以单独使用 NMOS、因为栅极以 VEE2为基准、因此可以轻松地对其进行控制。

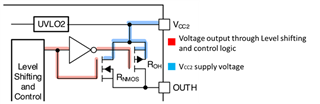

图3:混合上拉结构-- UCC53x0S

让我们看看混合上拉在开通过程中是如何工作的,如图3所示。 最初、OUTH 为低电平。 当电压通过电平转换和控制逻辑时、它将采用两条路径。 第一个是通过反相栅极、表示 PMOS 栅极的驱动器。 在应用 VCC2的情况下,PMOS 将在线性运行模式下运行,。 第二条路径是通过 NMOS、 当施加 VCC2且 OUTH 最初为低电平时、通过栅极源的电压将高于阈值电压、这也将导致 NMOS 以线性运行。 因此、导通相位输出电阻是并联组合 RO || RNMOS。

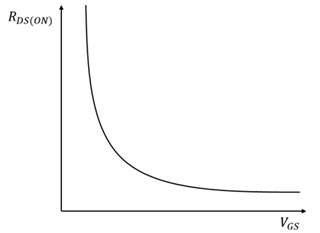

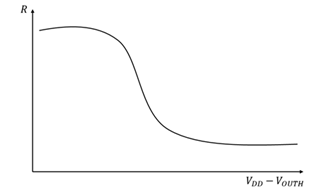

图4显示了 RDS (on) 与 VGS 的关系。 NMOS 的导通电阻随着 VGS 变小而增大、即随着 MOSFET 随着 OUTH 升高而进入截止区域。 另一方面、由于其栅极电压以 VCC2为基准、PMOS 导通电阻会随着 OUTH 的上升而保持不变。 这有助于在米勒平坦区域最需要时提供最高的峰值拉电流。

图4:(NMOS) Rds-on 与 VGS

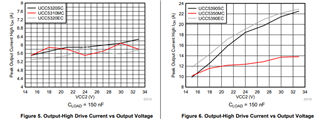

数据表中所述的漏源导通电阻在输出已经导通的条件下给出。 如图5所示、当输出电压接通时、PMOS 和 NMOS (RDS (on))的组合电阻最大。 因此、当 VDD 和 VOUTH 之间的差异 最大时、上拉的有效电阻看起来比导通瞬态期间的实际值大。

图5:Rds-on 的混合结构,用于 Lo || RNMOS 的并联组合

当输出已经打开时,上拉电阻的输出电阻等于卢武铉。

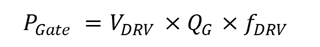

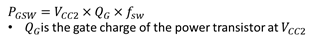

峰值电流是给定时间点期间的最大电流、对于栅极驱动器、峰值发生在开启或关闭的初始瞬态期间。 从栅极驱动器的输出到 MOSFET 或 IGBT 的栅极的电阻决定了峰值电流以及栅极驱动器中耗散的功率(和热量)。 当输出端的容性负载较大时、下面公式中表示的栅极电荷损耗将更高。 如果没有栅极电阻、所有栅极电荷损耗都会在栅极驱动器中耗散。

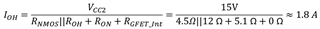

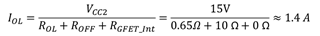

UCC53x0具有不同的变体、具有不同的驱动强度和引脚配置。 例如、UCC5320SC 的输出级具有分离输出。 峰值拉电流 IOH 由 VCC2 和 ROS || RNMOS 决定 、而峰值灌电流 IOL 由 VCC2和 ROL 决定、此外还添加了外部导通和关断栅极电阻器。

我们可以获得外部参数、以作为计算峰值拉电流/灌电流的示例、请参阅数据表中的第8.11节(电气特性)。

|

参数 |

最小 |

典型值 |

和功能 |

|

IOH 峰值拉电流 |

2.4 |

4.3. |

A |

|

IOL 峰值灌电流 |

2.2. |

4.4. |

A |

表2:UCC5320SC 峰值拉电流/灌电流

此外、我们还可以从 下图所示的数据表中的第10.3.3节中获得电阻值 RNMOS、ROH 和 ROL。

|

参数 |

RNMOS |

卢候选人 |

ROL |

和功能 |

|

UCC5320SC |

4.5. |

12. |

0.65 |

电阻 |

表3:UCC5320SC 导通电阻

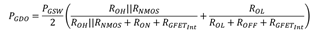

计算预期峰值拉电流和灌电流所需的公式可在数据表的第11.2.2.2节中找到。 外部导通电阻 RON 和功率晶体管内部栅极电阻 RGFET (INT) 可降低峰值源电流、如下面的公式所示。 从上表中、我们可以使用 UCC5320SC 参数值作为示例来计算预期峰值和灌电流。

同样、下面的公式用于计算灌电流拉电流。 外部关断电阻 ROFF 和功率晶体管内部栅极电阻 RGFET (INT) 可降低峰值灌电流、如下面的公式所示。

从数据表中、我们可以获得有用的指南、以确定栅极驱动器性能的典型能力。 但是、外部栅极驱动电阻器等外部因素会影响行为、因此应注意数据表的其他部分。 要评估 IGBT/MOSFET 不同负载下输出高驱动电流的性能、请参阅数据表中的图5和6。

具有栅极驱动器的目的是高效地打开和关闭功率器件。 通过这样做、我们会经历因开启和关闭 FET 而导致的开关损耗。 开关损耗将随偏置电压的升高而增加、这会相应地增加驱动电流并降低系统效率。 因此,栅极驱动器必须以最小的损耗进行切换。

有多种因素可能会影响栅极驱动器的功率损耗;第一个因素是静态功率损耗、第二个因素是开关操作损耗、第三个因素是输出级的损耗。

漏源导通电阻 RDS (on) 对栅极驱动器的功率耗散起着重要 作用、如前文所述、RDS (on)是 RON || RNMOS 的并联组合、根据上面的公式、我们可以看到 RDS (on)越小、输出级的栅极驱动器损耗就越小。

此 E2E 说明了 OUTH 具有比 OUTL 更高的有效电阻的原因。 使用混合上拉结构、我们的栅极驱动器能够在米勒平坦区域提供峰值电流、从而降低开关损耗。 此外、本报告还提供了用于计算开关功率耗散的公式、这些公式对于确定栅极驱动器可以开关的最大开关频率和最大栅极电容至关重要。 功率耗散由 RDS (on) 和其他因素决定。 由于 RDS (on) 是 ROS || RNMOS 在 混合上拉结构中的并联组合、因此功耗 最小化。