主题中讨论的其他器件: PMP9208、 PMP11753、 PMP

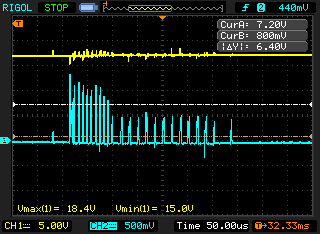

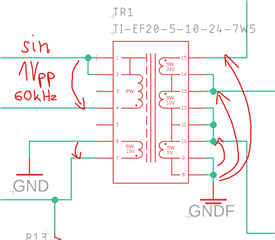

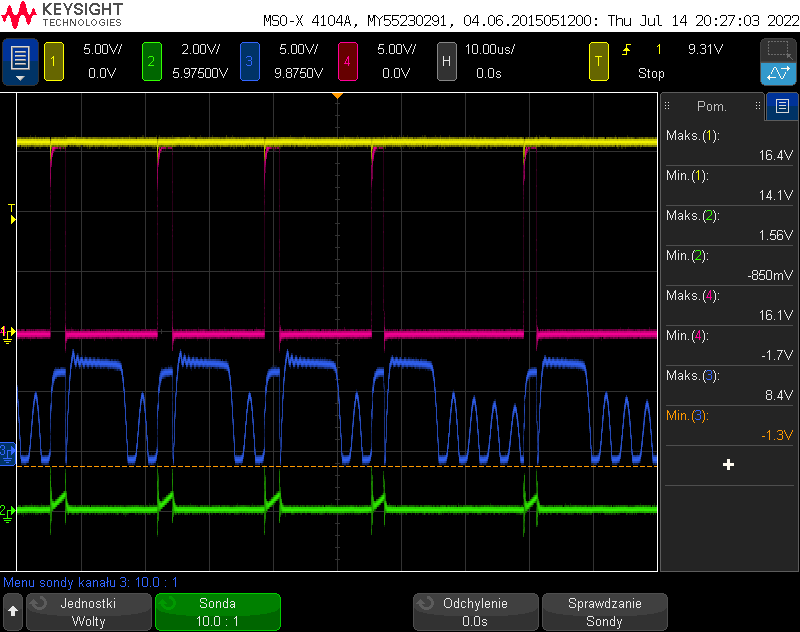

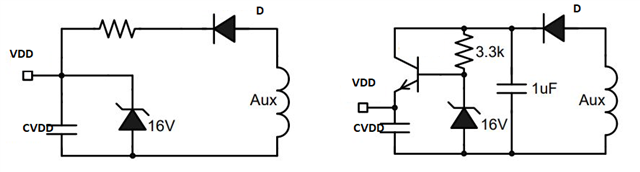

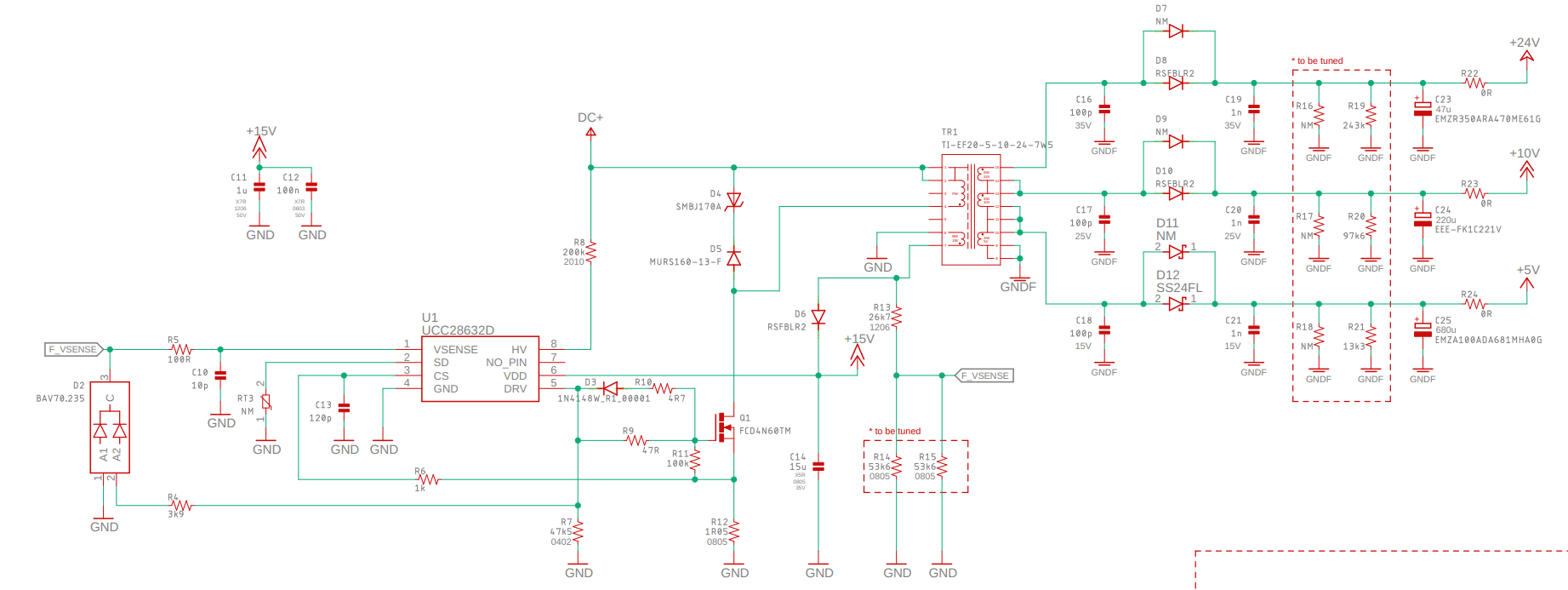

我遇到了基于 WEBENCH 和 UCC28632应用手册设计的反激式转换器问题。 请参阅随附的原理图。 转换器在230VAC (整流后为320VDC)下工作。 转换器的变压器旨在使辅助绕组产生+15V 电压。 次级侧的输出电压应为:+24V、+10V 和+5V。

我可以观察到转换器的3种工作模式:

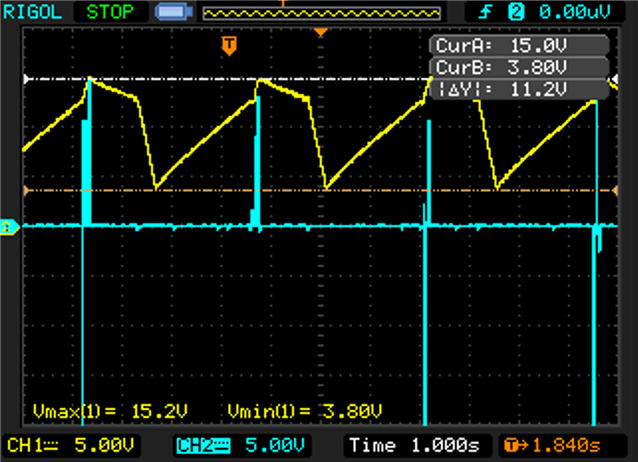

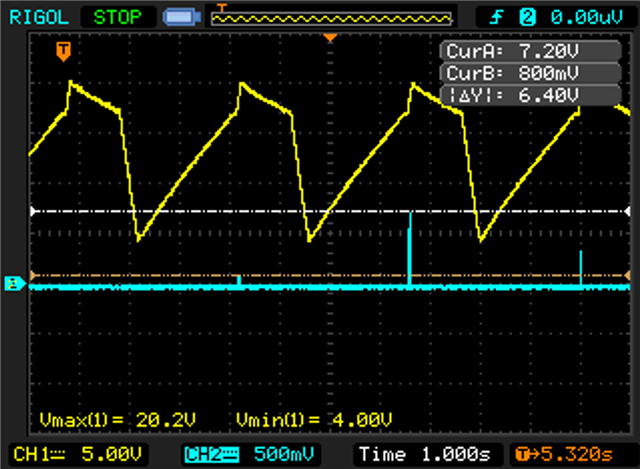

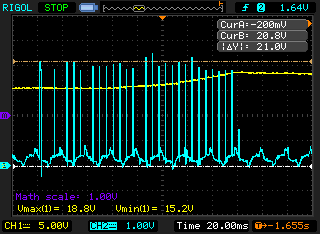

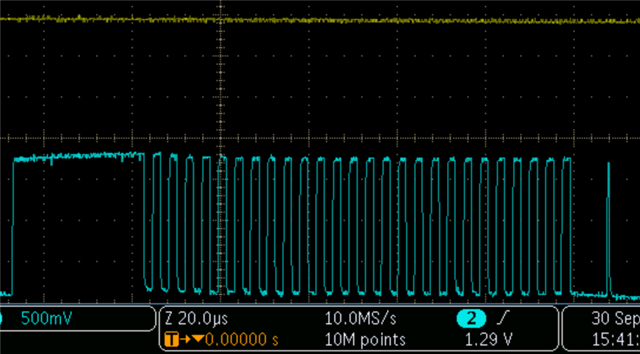

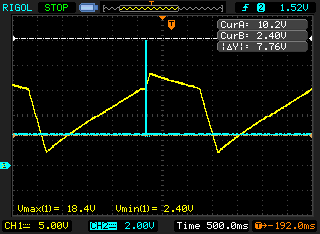

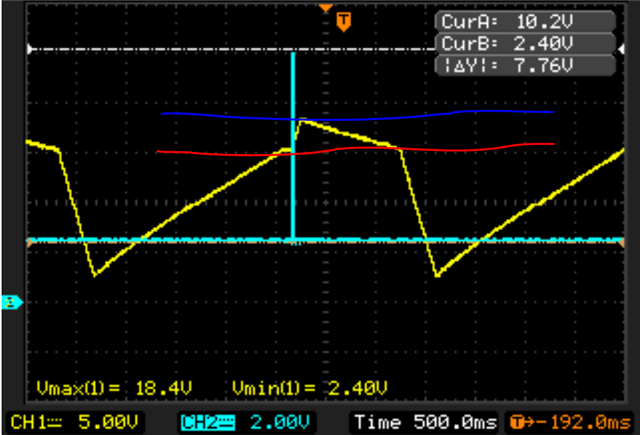

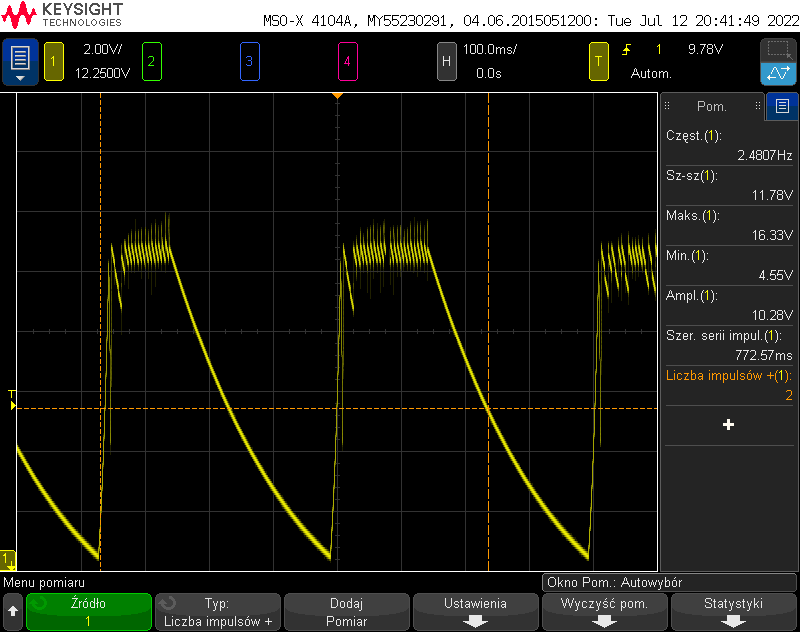

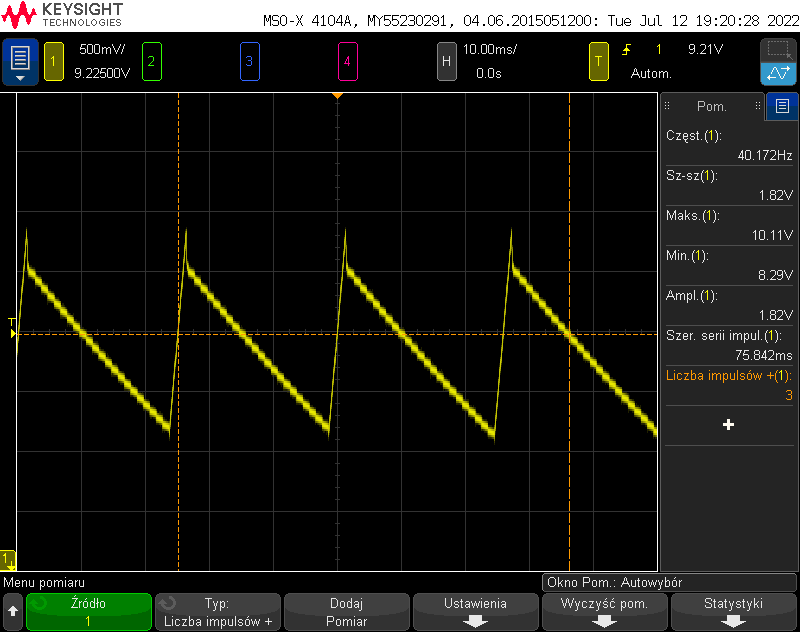

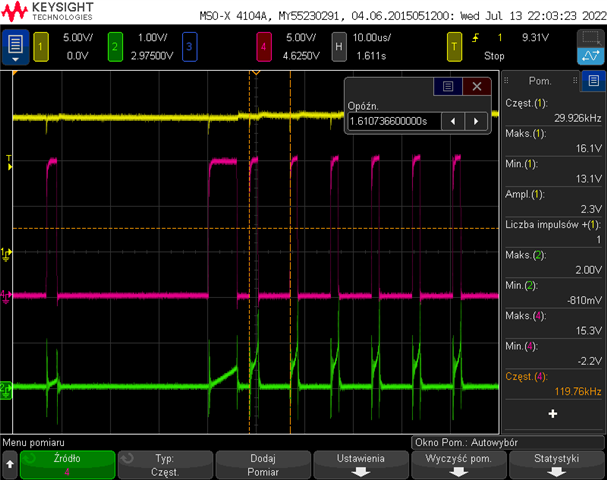

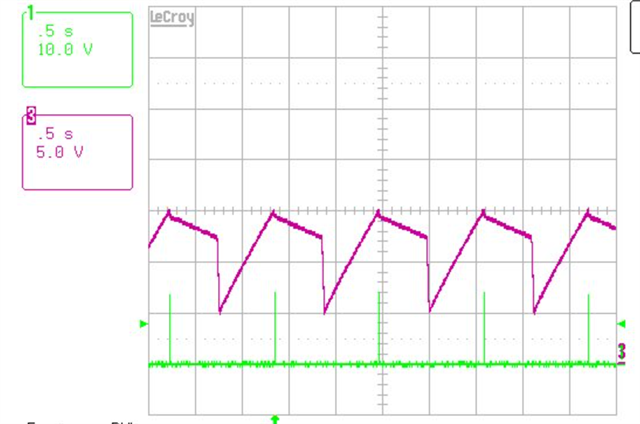

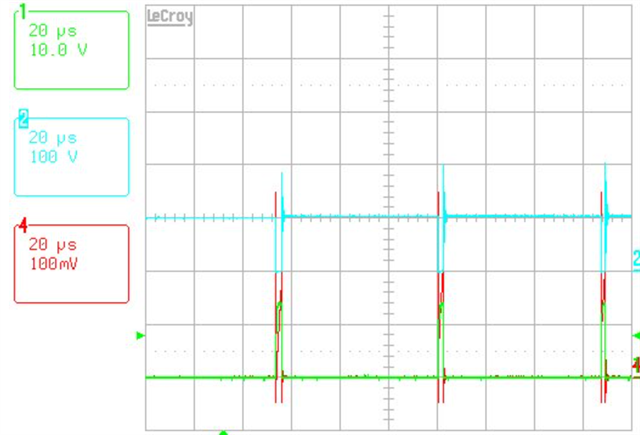

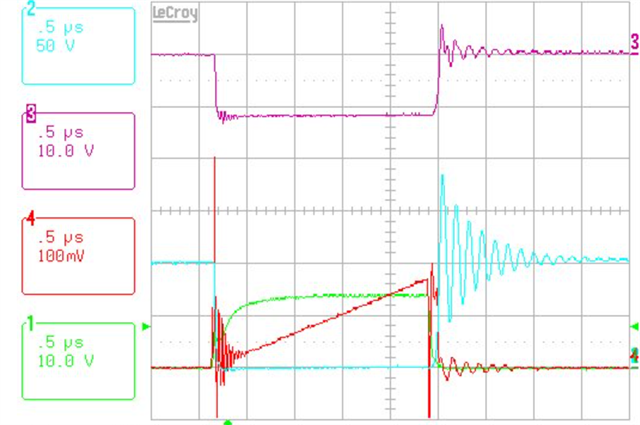

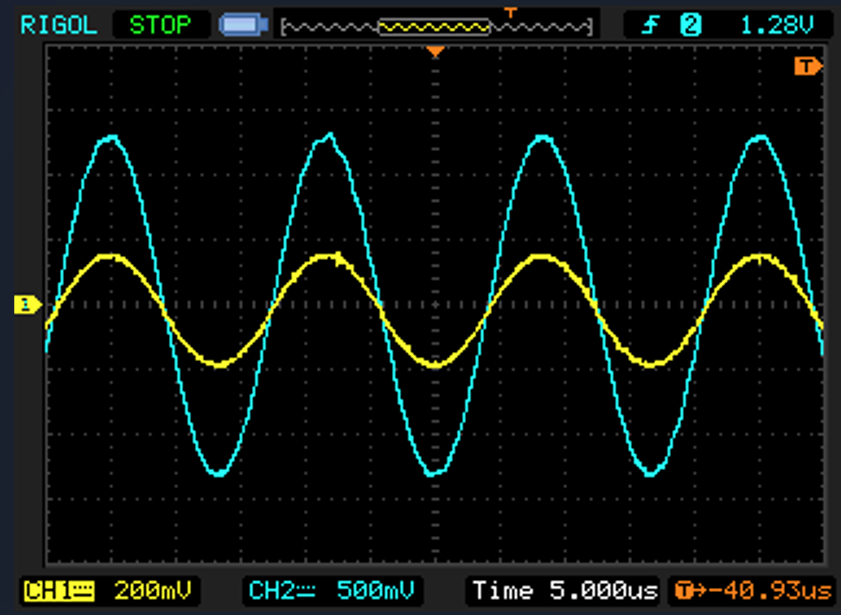

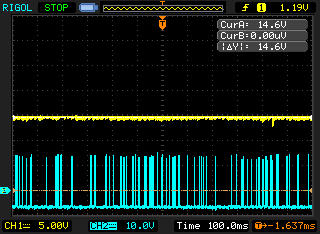

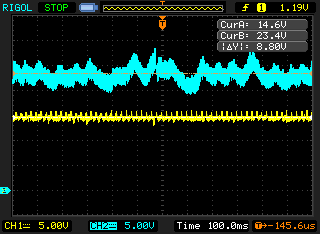

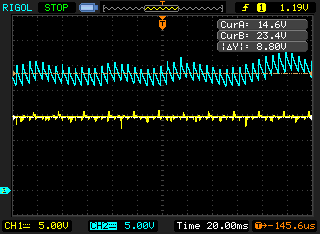

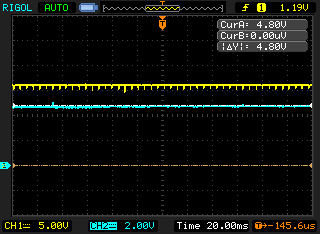

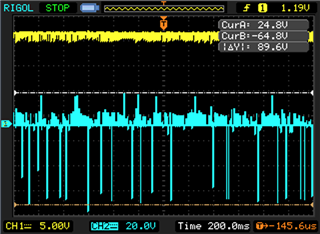

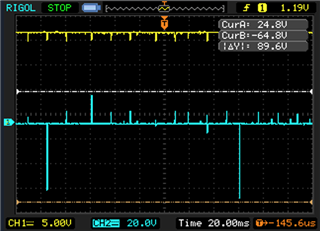

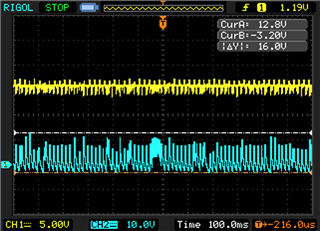

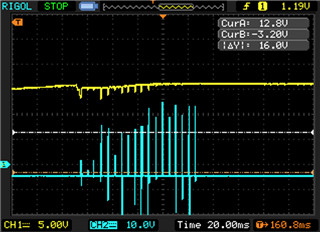

1.当次级输出被载入并且辅助输出(15V)未被载入时、我观察到输出上的正确电压(24、10、5)、但是连接到振荡器的+15V 辅助输出显示出波动的电压、纹波大约为7V 至14.5V。

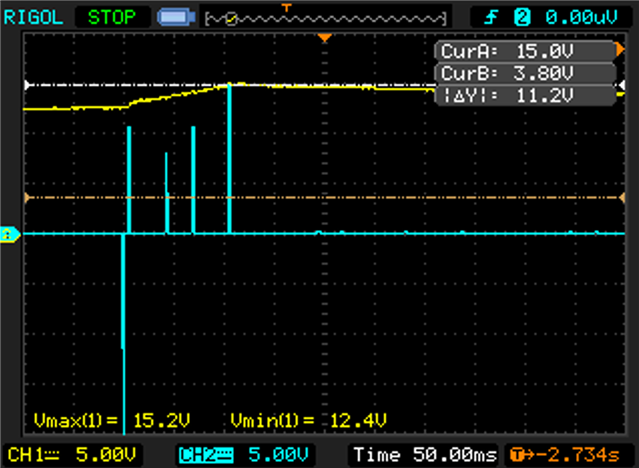

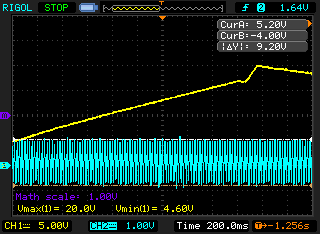

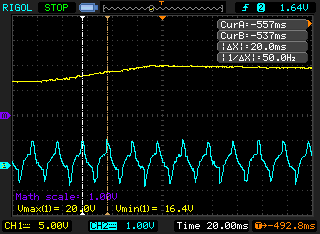

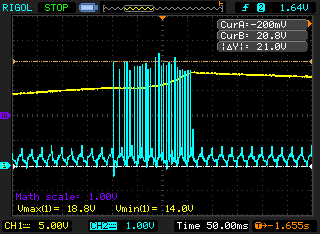

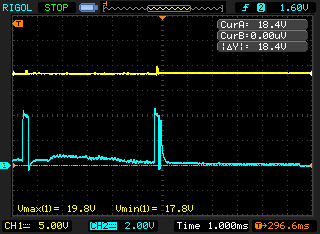

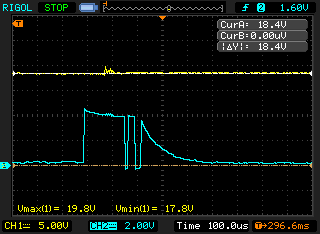

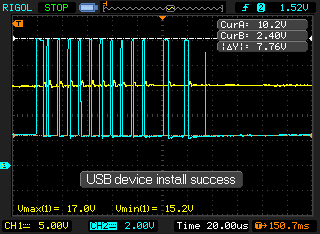

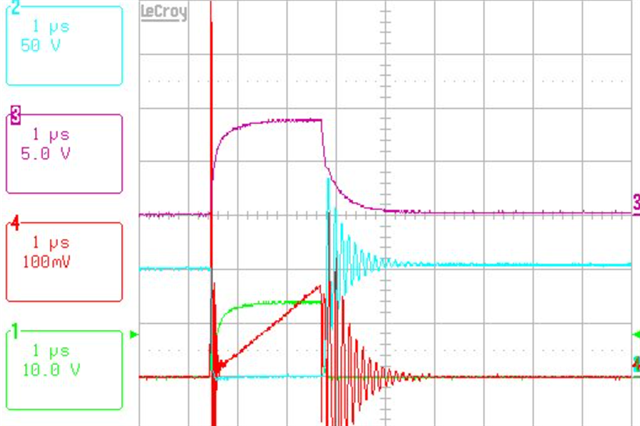

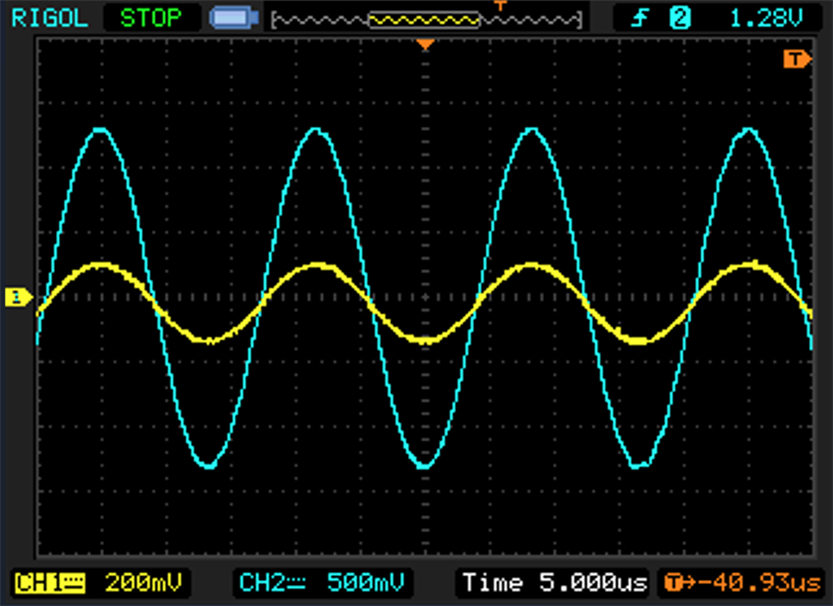

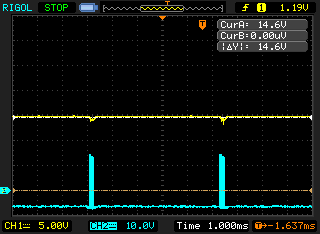

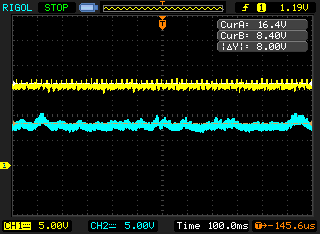

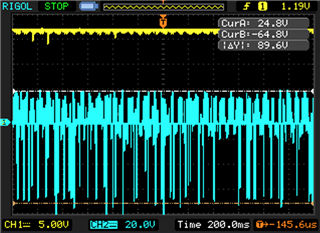

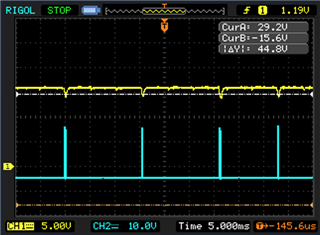

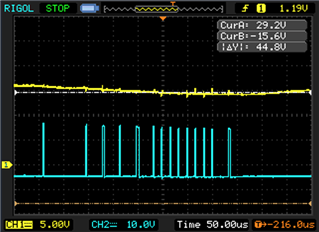

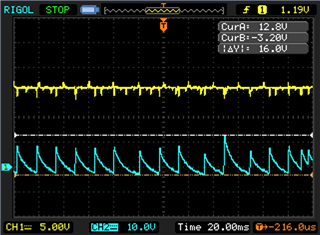

2. 当转换器输出被加载、辅助输出(15V)被10k 电阻器加载时、我观察到辅助输出上稳定的14.5V 电压、但次级输出(24、10、5)上的电压显著下降。

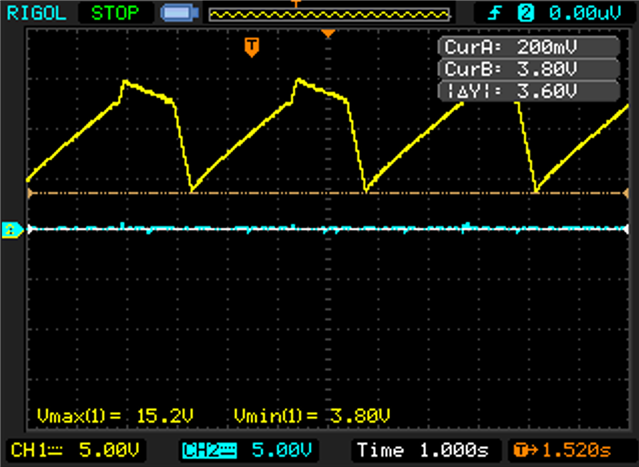

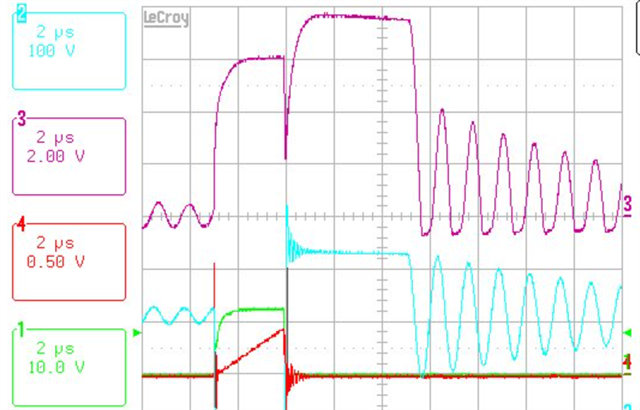

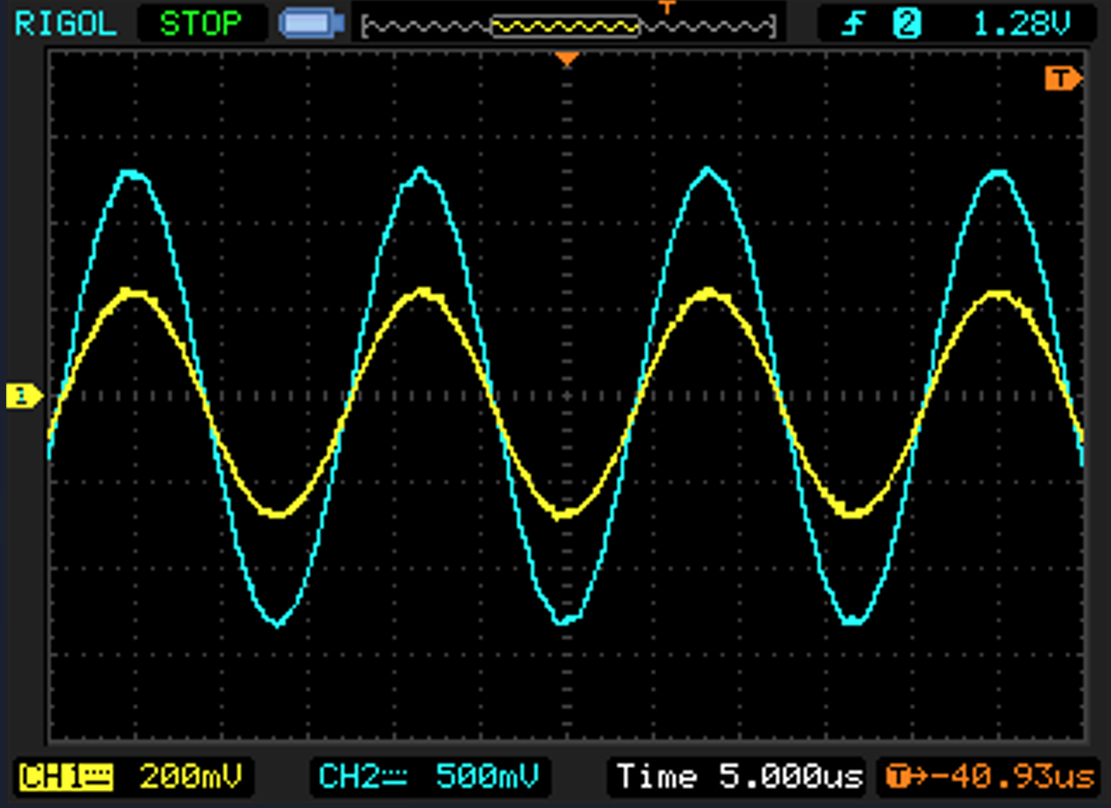

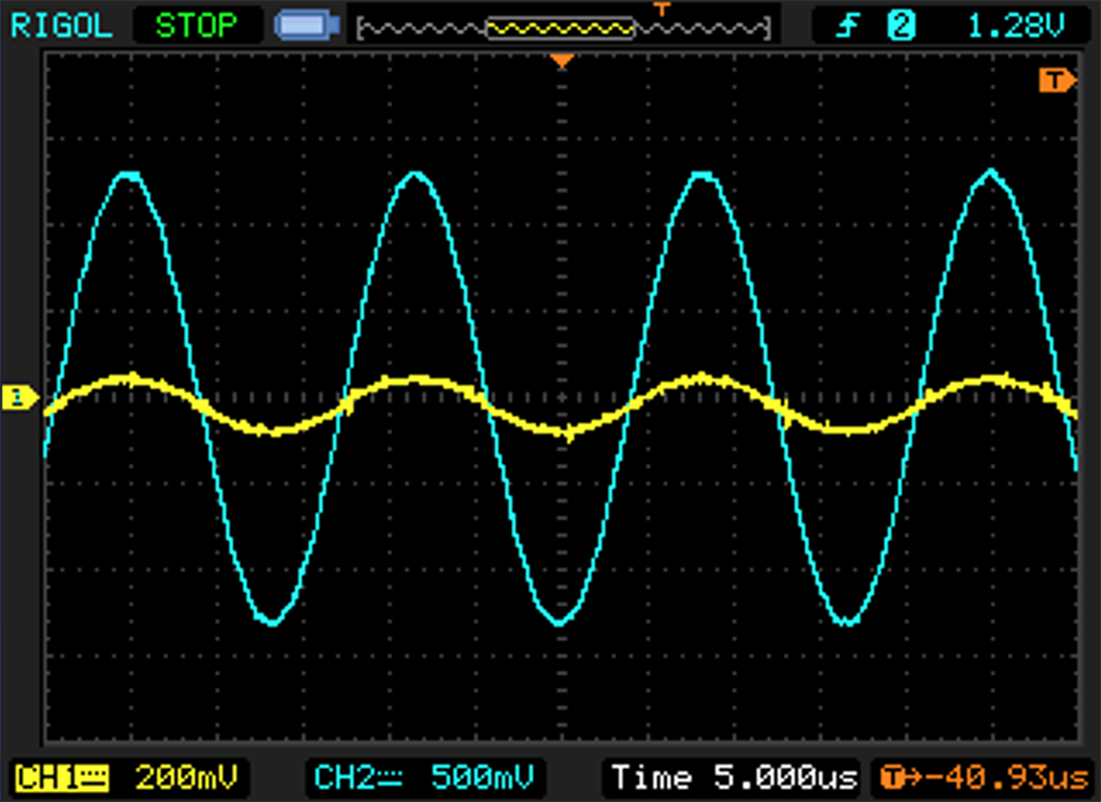

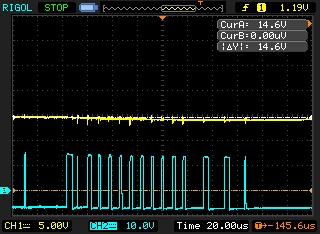

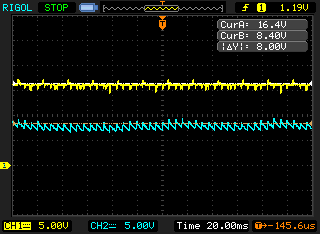

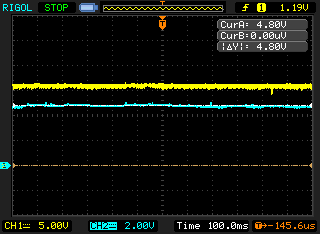

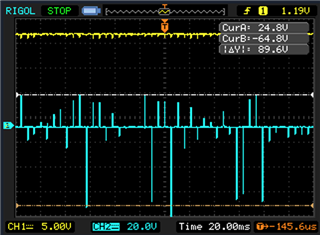

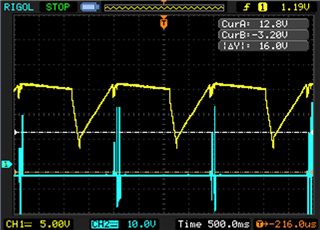

最后、当辅助输出加载10k 且所有辅助输出完全未加载时、我观察到辅助输出上稳定的14.5V 电压、而次级输出上的电压正确(24、10、5)。 一旦我将负载连接到任何次级输出、我就会在次级输出上松开正确的电压。

电阻器 R6、R7、R11、R12、R14、 R15、R13、R19、R20、R21未解决问题。

此设计可能存在什么问题、如何在辅助输出端实现稳定的14-15V 电压以及在负载次级输出端实现正确电压?

感谢你的帮助。

Pawel