您好!

请您就以下设计提供一些反馈。

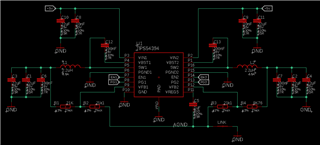

TPS54394

1V1 @ 3A

1V5 @ 3A

大多数器件的额定值都在原理图上。

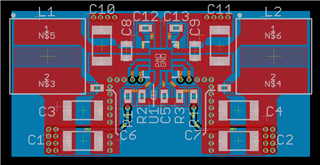

L1 & L2 = ABRACON ASPI-6045T-2R2N-T

布局如下:

有些内部层未显示、但它们是实心 GND 覆铜。 我是否应该释放电感器下的 GND 覆铜? 我看到了相互矛盾的建议。

我拆分了5V 输入、因此它们不共享输入电容器、每个输入都有自己的电容器。 这是一个好主意、还是我应该将其全部倒出来?

我本来希望高频滤波器输入电容器更靠近输入引脚、但它们不会连接到顶部的 GND 覆铜区。 他们在哪里看起来还可以吗?

我对从开关节点到输入电容器下方的电感器的覆铜宽度有点紧张。 但我认为这是最佳的折衷方案吗? 有什么想法?

非常感谢、

G