您好的团队:

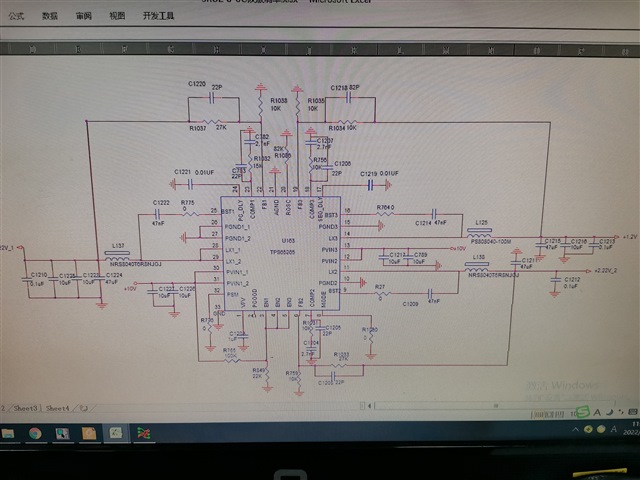

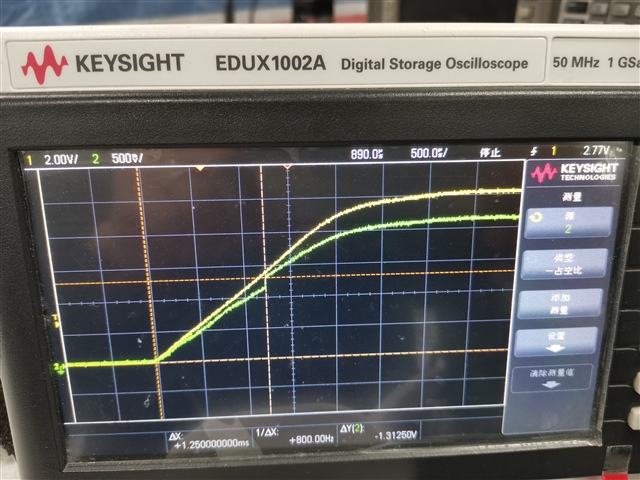

我的客户使用 TPS65265器件并反馈 BUCK1/2/3没有输出。 SCH 以及 PVIN 和 EN 的波形如下所示。

在我检查规格时、客户尝试悬空 MODE 引脚、它工作正常。

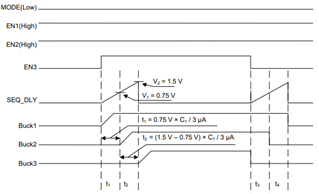

但我仍然 不清楚 Mode、UVLO 和 Enable 之间的逻辑。

查询:

我计算的 Vstart 和 Vstop 基于100K 和22K、Vstart 为6.09V、Vstop 为5.61V。 如波形所示,PVIN 未达到6V,但使能引脚已达到1.2V。 因此我认为、当 PVIN 不稳定、但 EN 为高电平时、没有输出是合理的。

->如果在模式连接到 GND 时使用此 UVLO 功能,则此 UVLO 设置和启用/自动加电序列逻辑如何工作? PVIN 似乎比 EN 具有更大的延迟。

->在浮动模式引脚时,如果 有任何限制阻止计时,降压1/2/3输出将正常工作? 或者它将忽略 UVLO?的设置