Other Parts Discussed in Thread: TPS61183

你好

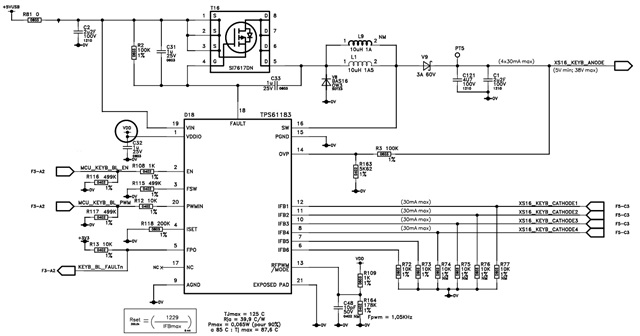

我使用 TPS61183 数据表第10页所示的隔离 FET 晶体管原理图将 LED 驱动器 TPS61183安装在电路板上。

我还遵循 了同一数据表第18页第8.2.2.3段中的建议。

输入电源为5V、连接到我的 PMOS 的电源(Si7617DN)。

源极和栅极之间有一个100kr。 栅极连接到 FAULT 引脚、输出(反向二极管和电感器)连接到 FET 的漏极。

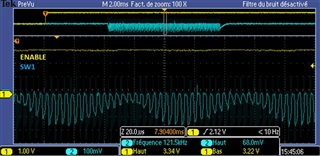

PWMIN 信号由频率为1KHz 的微控制器和可变占空比控制。

使用4个 LED 灯串(IFB1..IFB4)、IFB5和 IFB6通过一个10千欧电阻器被拉至0V。

EN 信号由微控制器驱动为高电平、该微控制器还在 PWMIN 引脚上提供 PWM 信号。

ISET 由一个200K 电阻下拉、以获得每串6mA 的电流。

我向 OVP 放置一个分压器(100K/5、62K)。

RFPWM/模式通过一个1K 电阻器被拉高。

RFSW = 499K 欧姆

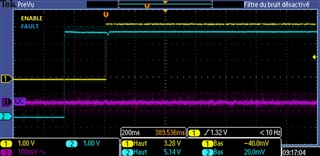

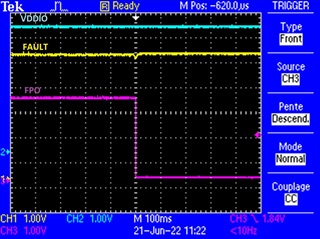

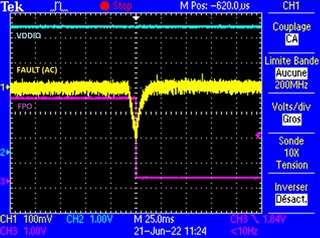

当我将 EN 信号设置为逻辑1时、我会看到 FAULT 引脚略有下降(小于200mV)、它会恢复到5V。

我的结论是、TPS61183的 FAULT 引脚未能将晶体管的栅极拉至0V。

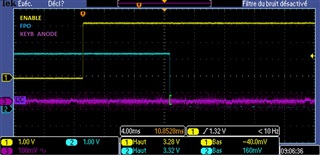

借助此原理图、TPS61183系统地进入错误状态、并将其 FPO 引脚拉至0 、输出 电压(连接到 LED 灯串阳极)为0V。

您能帮我解决什么可能导致此错误吗?

此致