Other Parts Discussed in Thread: TPS546D24, TPS546D24A

主题中讨论的其他器件:TPS546D24、

您好的团队:

最近、我发现 TPS546D24有问题。 目前、使用3个并联器件输出120A 电流。 当两个器件在-20摄氏度的低温下运行时、电压将突然下降至0V、然后恢复。 在这种情况下没有过流,负载约为40A。 稍后、在我将 BOOT 引脚的0.1uF 电容器更改为0.01uF 后、问题不再出现在下一个1周温度周期测试中。 我想问的是、更改该电容值后会受到什么影响? 我仍然不明白为什么在改变电容值后它变得更好。 我担心将来会有问题。 手册建议将其连接到0.1uF。

或者、在这种情况下、我是否可以使用其他方法进行双重检查? TKS、以获取您的支持。

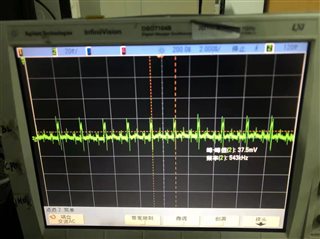

输出电压波形如下所示。 在一个温度周期测试中、它在0.5小时内显示3-4次。