您好、TI 专家、

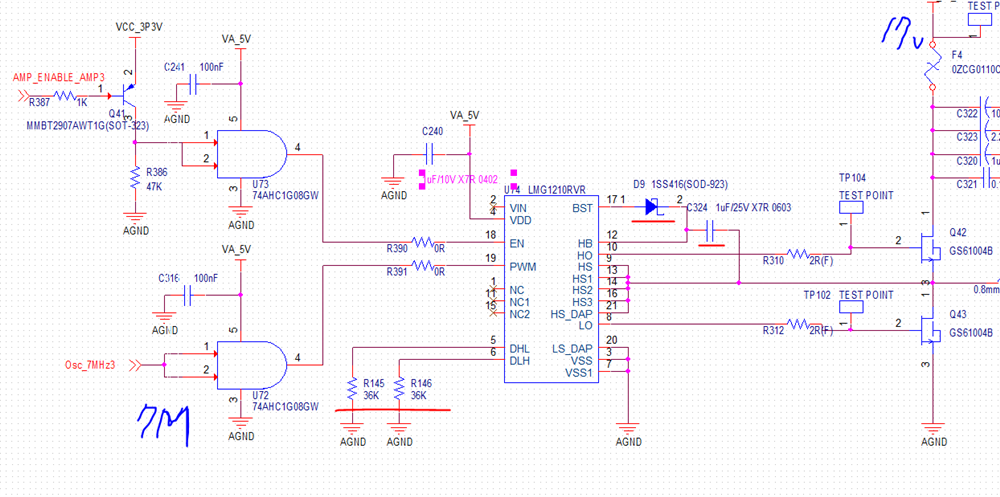

我的客户使用 LMG1210绘制了原理图。 您能评论一下吗?

下面是一些问题;

1、输入信号(PWM)为7MHz (低0V、高5V)。R145和 R146的优化值是什么?

2.您可以在 BST 和 HB 之间看到 D9。客户想要使用1SS416、哪个 VR 为30V。电路可以吗? VR 是否有任何最小值?

3.我的客户为 EN 引脚提供了 LVTTL 信号。可以运行吗?

请检查这些问题。 谢谢。

此致、

Chase

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、TI 专家、

我的客户使用 LMG1210绘制了原理图。 您能评论一下吗?

下面是一些问题;

1、输入信号(PWM)为7MHz (低0V、高5V)。R145和 R146的优化值是什么?

2.您可以在 BST 和 HB 之间看到 D9。客户想要使用1SS416、哪个 VR 为30V。电路可以吗? VR 是否有任何最小值?

3.我的客户为 EN 引脚提供了 LVTTL 信号。可以运行吗?

请检查这些问题。 谢谢。

此致、

Chase

你好,Chase

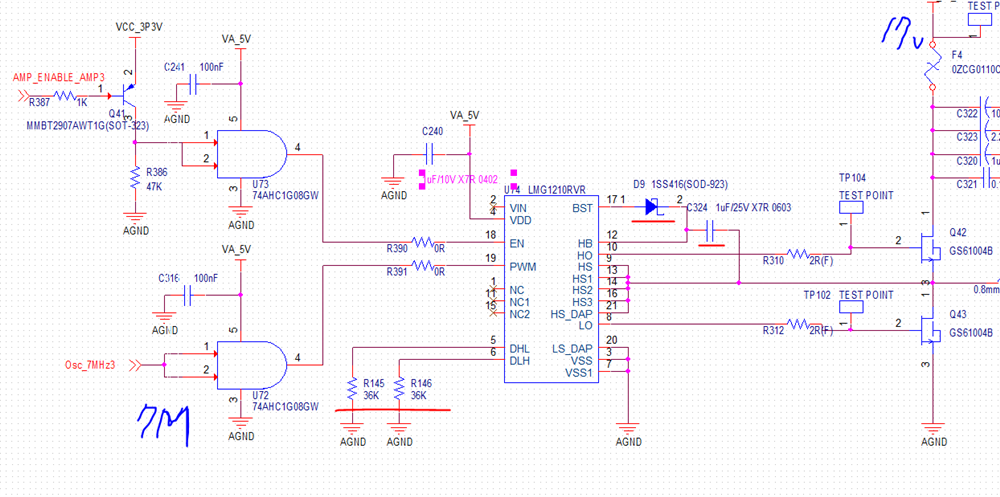

1.对于0.8ns 的最小死区时间,典型值使用1.78Mohm 电阻器

2. VR 需要高于 VHB-VDD。这应该接近 Vbus。 也会出现一些过冲瞬态、但对于17V +瞬态、30V 应该足够。

3.只要 EN 引脚在驱动器运行时获得稳定的信号、就不会出现问题。

进一步的注释:自举电容器(C324)对于被驱动的 FET 过大。 在这种情况下、100nF 电容器应该起作用。 此外、VDD 旁路电容(C240)必须至少为自举电容的10倍。如果 C324切换到100nF 电容、C240的电流1uF 就足以满足应用需求。

谢谢、

Daniel W

尊敬的 Daniel:

感谢您的支持。 我将与客户讨论、如果有其他问题、请回复。

这里有一些关于布局的问题。 可以帮我检查一下吗?

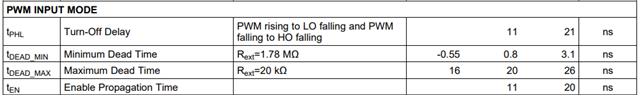

如您所见、数据表中的布局示例显示 VSS 散热焊盘通过7引脚连接到顶层的其他 VSS。

但在客户的布局中、 VSS 散热焊盘通过3号引脚连接到顶层的其他 VSS。

我们必须确认这是可以的、或者可能有一些问题。 (因为他们没有足够的时间、所以在制造光绘和真实 PCB 之前、应尽量减少风险。)

请检查此问题。 谢谢。

此致、

Chase