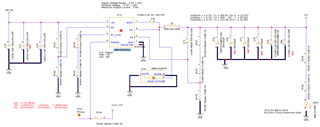

以下电路是原型设计。

VIN = 48V

VOUT = 24V

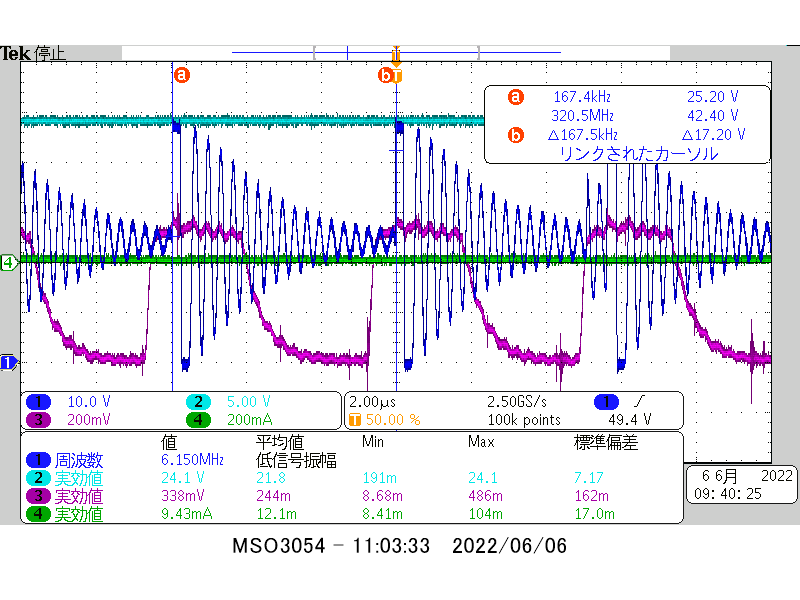

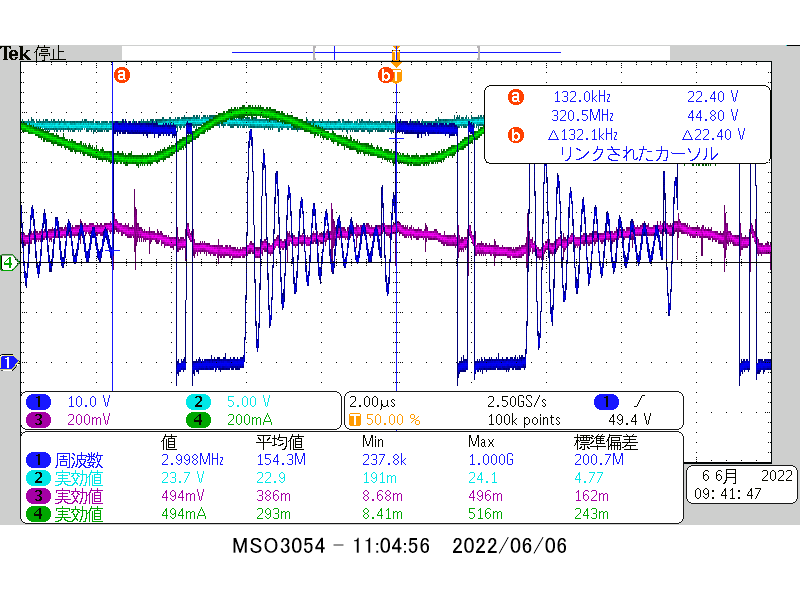

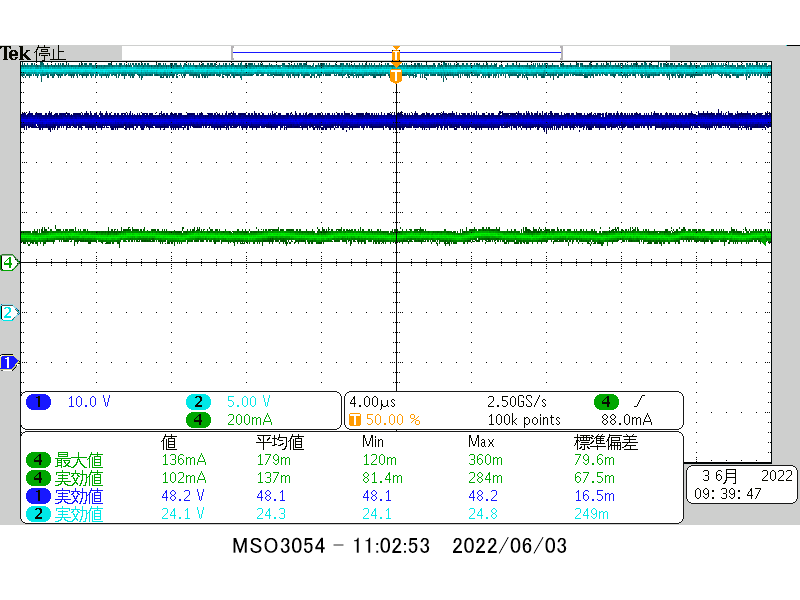

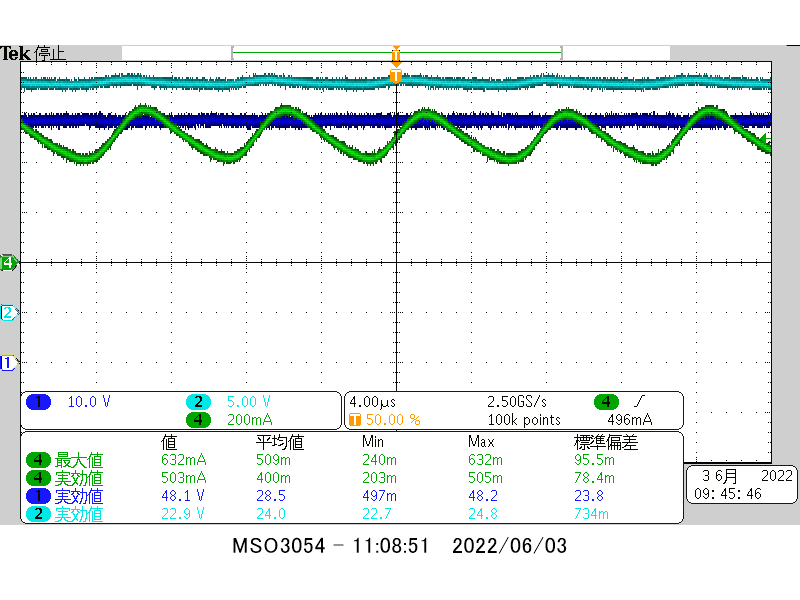

根据测量结果、输出电压根据负载降低。

100mA =输出电压:24.1V

500mA =输出电压:22.9V

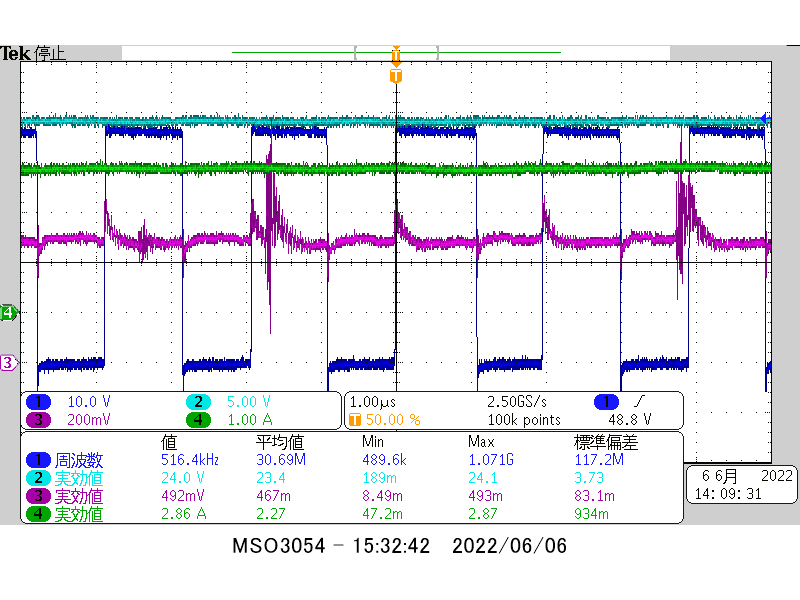

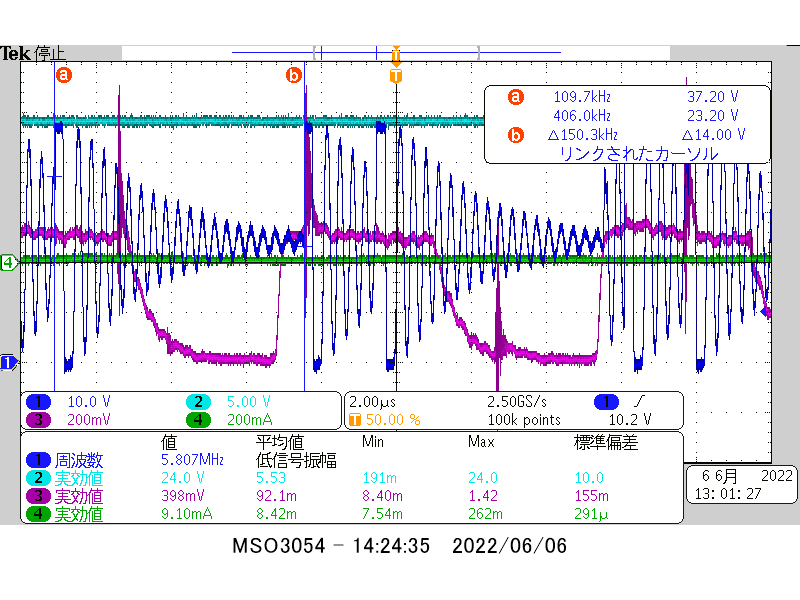

1Ch = Vin

2Ch = Vout

3通道= Iout

如果在"WEBENCH"中设置 Vin=48V、Vout=24V、Iout=3A、Temp=30°C、则 CFF=560pF、最好更改为220pF。

在进行此修改后、我重新测量了、但即使在 Iout=1A 左右的条件下、Vout=22-23V。

请告诉我应在哪里进行更正。

此致。