主题中讨论的其他器件:TPS54202

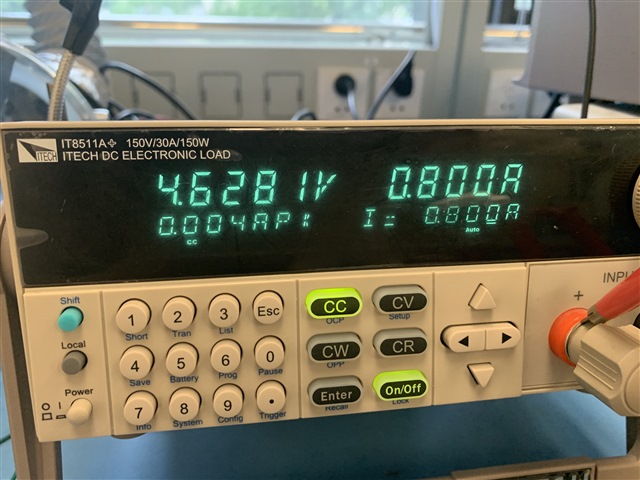

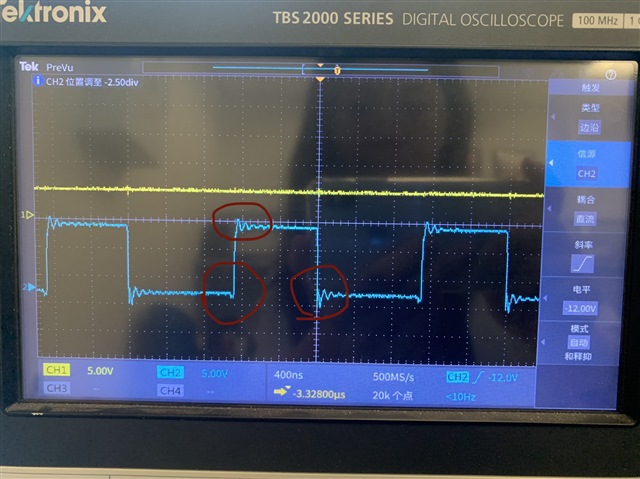

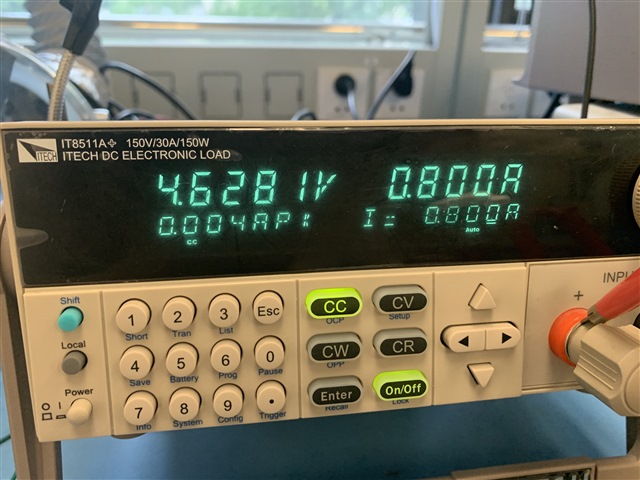

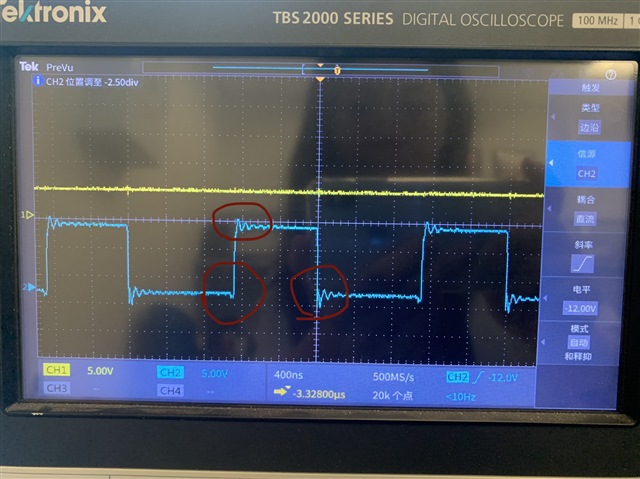

今天我在测试 TPS54202EVM 时发现、当 Vout=4.628V、Iout=0.8A 时、Vsw 的波形高于。 我不明白我用红线圈出的位置。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

今天我在测试 TPS54202EVM 时发现、当 Vout=4.628V、Iout=0.8A 时、Vsw 的波形高于。 我不明白我用红线圈出的位置。

您好、Skylar、

对于第1部分、负电压平台是由死区时间内低侧 MOSFET 中体二极管导通引起的。

对于第2部分、上升沿的振铃是由 Vin 引脚和 Cin 之间 PCB 布线中存在的寄生电感引起的、该电感由高 di/dt 引起。

对于第3部分、下降沿的振铃是由 PCB 迹线中 GND 引脚和 PCB GND 端子之间存在的寄生电感引起的。 根本原因与第2部分相同。

希望我的分析能有所帮助!

BTW、您能否简要介绍测试 TPS54202EVM 的原因? 此部件是否应用于客户应用?

BRS

Zixu