尊敬的 TI 支持团队、我对 TPS26631的 PGTH 功能有疑问。

PGOOD 在 VPGTHR 变为高电平时是否存在任何条件?

当 PGOOD 为低电平时、PGOOD 是否会在 VIN = Vout 而不 是 PGTH 设置的电压时变为高电平?

谢谢

此致、

渡边

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 TI 支持团队、我对 TPS26631的 PGTH 功能有疑问。

PGOOD 在 VPGTHR 变为高电平时是否存在任何条件?

当 PGOOD 为低电平时、PGOOD 是否会在 VIN = Vout 而不 是 PGTH 设置的电压时变为高电平?

谢谢

此致、

渡边

尊敬的 Watanabe:

请在下方查找我的评论

PGOOD 在 VPGTHR 变为高电平时是否存在任何条件?

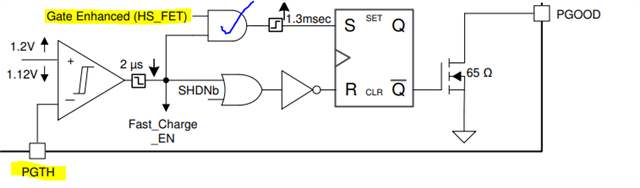

Rakesh:- 为了使 PGOOD 保持高电平、必须完全增强内部 FET 以及 PGTH >1.2V

当 PGOOD 为低电平时、PGOOD 是否会在 VIN = Vout 而不 是 PGTH 设置的电压时变为高电平?

Rakesh:-否

此致、

Rakesh

谢谢 Rakesh

请告诉我以下三个问题。

(1)上面提到的栅极是指方框图的哪个部分?

(2)在上面的方框图中、当 PGTH > 1.2V 时、PGTH 的迟滞比较器的输出变为低电平、PGOOD 不变为高电平?

(3)当 SHDN 端子断开时、RS 触发器的输入端子 R 是否始终为低电平?

通过检查我们的系统、当 SHDN=OPEN 且 PGTH 低于阈值时、PGOOD 变为低电平。

在方框图中、如果 R 始终为低电平、PGOOD 似乎永远不会变为低电平、因此行为不匹配。

此致、 Watanabe

您好、 Rakesh、

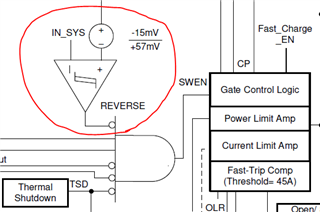

1A)我认为、在启动期间、当 Vout 达到 Vin (Vin_sys)时、Swen 会变为高电平、但在方框图中、比较器的输出相反、因此在 Vout 达到 Vin (Vin_sys)之前、Swen 会变为高电平。 我的想法是否正确?

2a)我明白了。 谢谢你。

3A)如果 SHDN 开路并在内部上拉至2.7V、SHDNb 将始终为高电平、因此无论 PGTH 的状态如何、或门输出都将始终为高电平。 或门输入的 SHDNb 是否反向? 还是输出 SHDNb 的比较器的极性相反?

此致、 Watanabe

您好、 Rakesh、

感谢你的答复。

1A)上述比较器输出是否仅在反向连接中变为1并在进入与门之前进行反向?

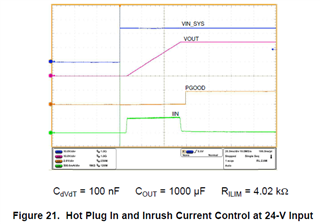

在这种情况下、我认为 PGOOD 会在启动时 Vout 开始上升的同时变为高电平。但是、在数据表的图21和我们的系统中、当启动时 Vin = Vout 时、PGOOD 会变为高电平、因此我认为它与方框图不匹配。

3a)我明白了。谢谢。

此致、 Watanabe

您好、 Rakesh、

感谢您的确保。

>我们的设计人员确认上述电源正常模块是正确的。 您能否逐步说明它不匹配的地方。

→确定。

μ・方框图操作(正常启动)

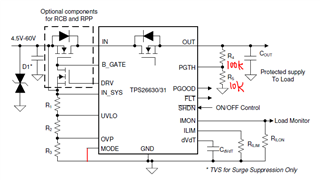

①SWEN Ω 在输入 Vin 后变为高电平、并超过 PORb 和 UVLO 阈值。

内部 FET 的②the Ω 栅极超过栅极控制逻辑中的 VIN+3V。

③At 在 FET 导通且 Vout 开始上升的同时(延迟为1.3ms)、它在 RS 触发器中设置、PGOOD 从低电平变为高电平。

・数据表和系统中的图21

Vout 完成上升后、PGOOD 变为高电平

(在确认时、PGTH 引脚的电阻如下所示)

此致、 Watanabe