大家好、

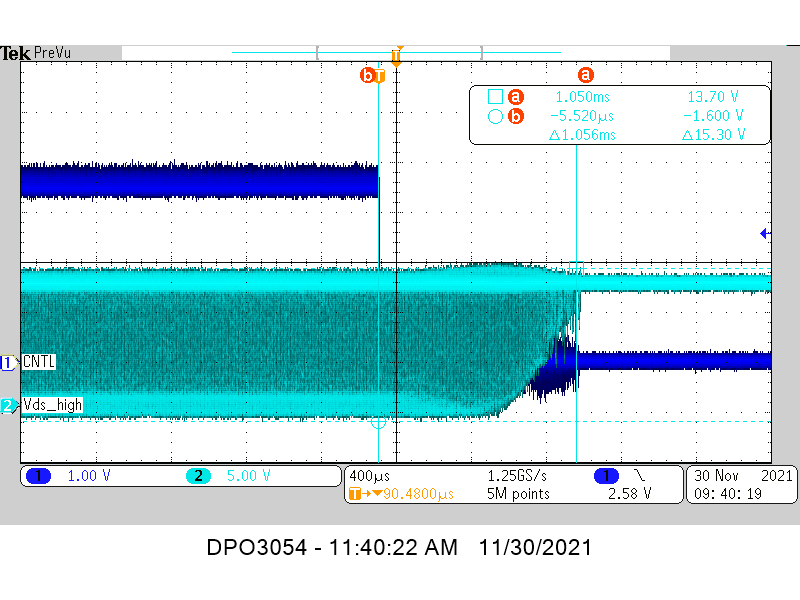

我测试 TPS546C23EVM、控制 CNTL 下拉电阻以禁用 TPS546C23的输出、并测试 SW 的输入电压(高 Mos VDS)

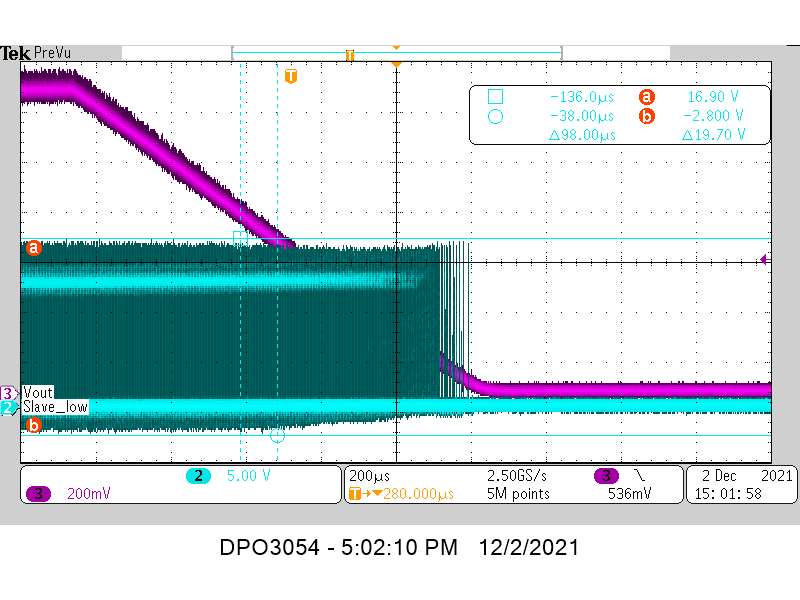

看到输出软关断时间为1ms、最终500us VDS 也增加了、我想确认我们的软关断控制机制是什么、为什么高 Mos VDS 会增加?

此致、

刘德华

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

TPS546C23的 TOFF_FALL 控制使开关转换器保持运行、同时在 TOFF_FALL 定义的时间段内、基准电压从稳压输出电压降至0V。 对于1ms、这意味着在1ms 内强制将输出电压从 Vout 放电至0V。

VOUT 下降期间 VSW 电压增加很可能导致输出电容放电电流(Vout x Cout / TOFF_FALL)超过负载电流、从而导致负电感器电流。 负电感器电流会导致死区时间电流从电感器流入 SW 节点并流经高侧 FET 的体二极管、而不是通过低侧 FET 从开关节点流入电感器。 在此死区时间内、高侧体二极管上的压降会增加 SW 节点上的电压。

Peter James Miller

您好 Miller、

昨天测试的波形错误。 我测试了高 Mos 的 Vds、但使用了较长的导线、这会引入干扰、因此图片是错误的;

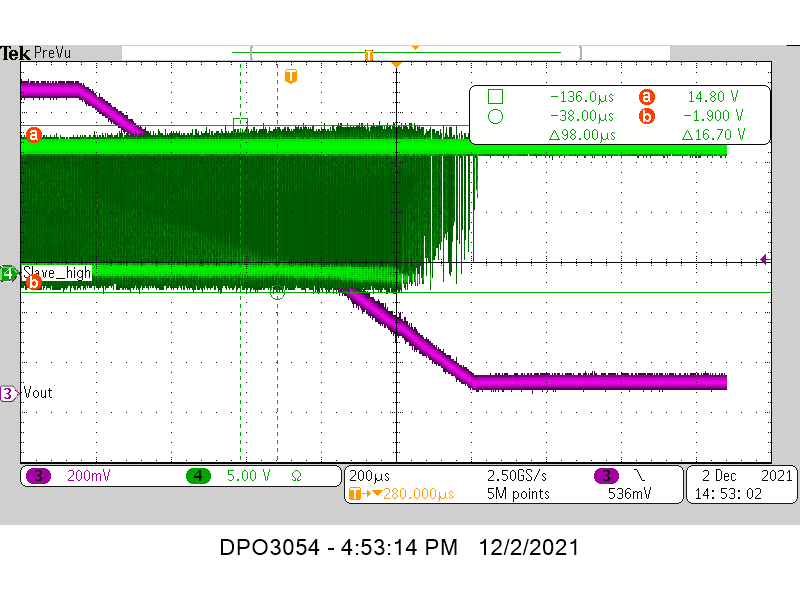

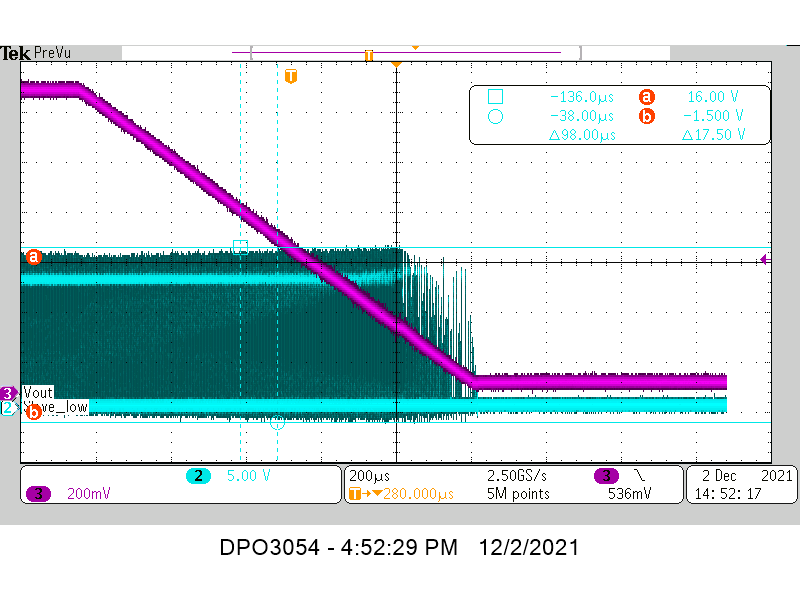

请参阅以下两个图、即高 Mos Vds 和 低 Mos Vds。 图1和图2、禁用器件时无负载。 您可以看到 、高 Mos 和低 Mos 的 Vds 均已上升。 您能否帮助解释它们上升的原因? 特别是高 Mos VDS、我看到大约1V 的电压上升;

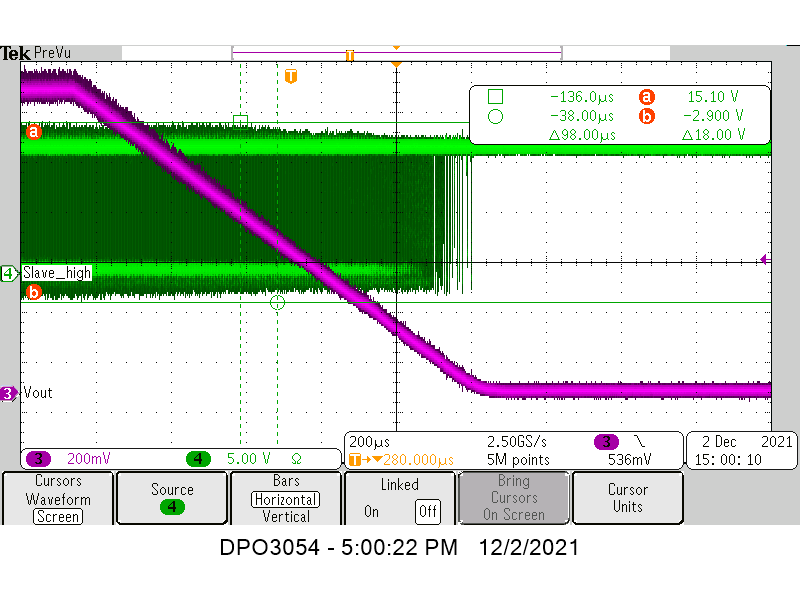

同时、下图显示了40A 负载、然后禁用器件。 您可以看到 、高 Mos Vds 的最高值已经下降、占空比正在缓慢下降;低 Mos Vds 的最低值、 SW 的负压也略有下降、占空比逐渐下降;我在这里如何理解? 禁用器件时、似乎有负载或没有负载、状态不同。 请帮我解决困惑、谢谢。

您所描述的是与我之前描述的现象相同的现象、并提供了一些其他详细信息。

当电感器电流为零安培时、峰值电感器电流在高侧 FET 关断时为正电流、电感器从开关节点消耗电流、直到低侧 FET 体二极管传导电流、从而在开关节点上施加负电压。 当低侧 FET 在谷值电流下关断时、谷值电流为负、电感器将电流驱动到开关节点、直到高侧 FET 体二极管将电流传导回 PVIN、从而导致峰值 SW 电压大于 PVIN。

当2,000μF 1ms 软停止计时和超过1 μ F 的输出电容充电至3.3V 时、平均电感器电流被强制为负电流、从而驱动更多电流通过体二极管并为 VIN 电容器充电、从而增加 VIN 和 SW 电压。

然而、当转换器提供40A 电流时、输出电容器放电所需的7A 电流不会导致负电感器电流、而只是正电感器电流更小。 转换器只需提供33A 的电流、而不是40A 的电流。 较低的电流会产生较少的振铃和较低的开关节点电压应力。