Other Parts Discussed in Thread: PMP30963, CSD18536KTT, CSD17318Q2, LM5152-Q1, LM5152EVM-BST, CSD17581Q3A, LM5176

主题中讨论的其他器件:PMP30963、 CSD18536KTT、 CSD17318Q2、 LM5152-Q1、 LM5152EVM-BST、 CSD17581Q3A、 LM5176

大家好、团队、

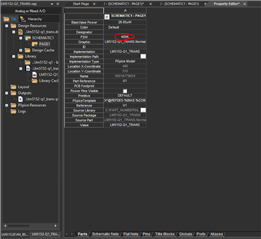

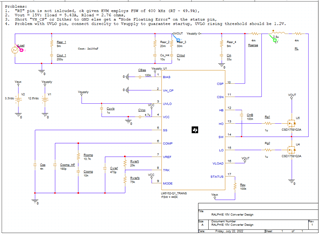

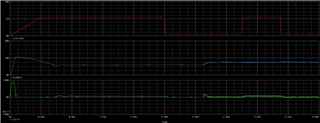

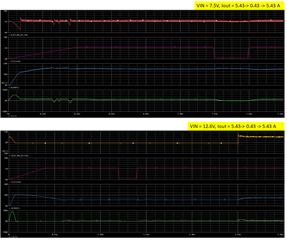

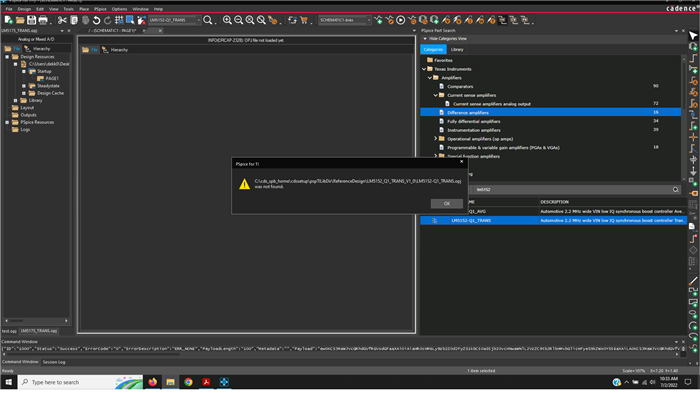

我的客户 在尝试打开部件参考瞬态仿真/设计时遇到以下错误(请参阅随附的图片)。

有没有关于如何解决这个问题的想法?

此致、

Renan