主题中讨论的其他器件:PMP30963、 CSD18536KTT、 CSD17318Q2、 LM5152-Q1、 LM5152EVM-BST、 CSD17581Q3A、 LM5176

大家好、团队、

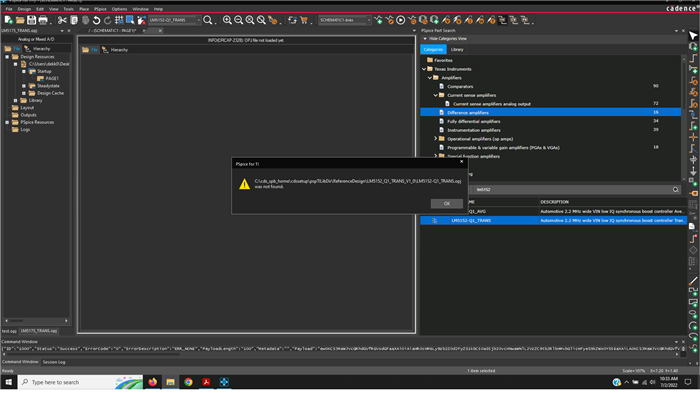

我的客户 在尝试打开部件参考瞬态仿真/设计时遇到以下错误(请参阅随附的图片)。

有没有关于如何解决这个问题的想法?

此致、

Renan

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、团队、

我的客户 在尝试打开部件参考瞬态仿真/设计时遇到以下错误(请参阅随附的图片)。

有没有关于如何解决这个问题的想法?

此致、

Renan

Renan、您好!

我刚刚检查了我们的 PSpice 库、遗憾的是、目前还没有支持 LM5152的 PSpice 参考模型。

相反、我建议使用 PSpice for TI 库中的正常 PSpice 瞬态模型(仅 IC)、或从产品页面下载一次、并获取快速入门计算器或参考设计(PMP30963)作为指导。

https://www.ti.com/product/LM5152-Q1#design-tools-simulation

https://www.ti.com/tool/PMP30963

如果您有其他问题、请告诉我。

此致、

Niklas

您好 Niklas、

祝你一切正常、感谢您的回答。 请参阅以下我的客户回复:

我使用 PSpice for TI 尽可能地重新创建器件的 EVM 模型/原理图。

我在"STATUS"引脚上看到以下奇怪的"浮动节点"错误(请参阅随附的图片)。

不确定为什么会出现此错误。 如果我将其连接到3.3V、接地或未连接、则会出现相同的错误。已附加完整的项目(请参阅附带的 zip 文件)。

是否有人会帮助我解决此错误?

e2e.ti.com/.../Help.zip

此致、

Renan

您好 Niklas、

你好。 当您 正在处理有关"浮动引脚问题"的第一个问题时 、请参阅下面我的客户提供的其他查询:

1.如何准确地确定部件"Rcom"、"comp "和"ch瑞士 法郎"? 我采用了"Quickstart Calculator"器件中的所有推荐组件。 我还理解这些组件是补偿器组件、但在做出补偿器决策并通过补偿器闭合环路(T)之前、必须首先确定系统的开环增益(Tu)。 我提出的原因是开环/闭环增益并不完全明显、即从反馈引脚到控制信号的路径。 通常、器件数据表对该路径进行了一些粗略的描述。 也许您团队中的某个人已经就这个主题编写了一份白皮书。 请告诉我。

2.还尝试为我的特定应用确定 N 沟道 MOSFET (请参阅随附的快速入门计算器 Excel 表格了解我的设置)。 器件 EVM 板采用了以下合适的超大器件:

NVMFS5C645NLWFFT1G

不再提供的功能。

通过查看 TI N 沟道 MOSFET、我发现了以下几点:

第一个是 csd18536ktt、它与 EVM MOSFET 非常匹配。

第二个是 csd17318q2、似乎是针对诸如此 boos 控制器器件的低 VGS 器件而设计的。

想知道 EVM 设计为何不采用 TI MOSFET?

TI 是否有合适的白皮书/工具来帮助确定适合我的特定应用的最佳 MOSFET?

此致、

Renan

Renan、您好!

下面是我这边的更新:

我仍然没有找到"悬空引脚"错误的来源。 我不认为模型中有错误、因为它的功能对其他电路来说还可以。 它可能是一些内部路径、这使得模型认为状态引脚在当前状态中处于悬空状态。

我将更深入地探讨、看看我是否能找到解决方案。

客户告知没有 RT 引脚。 即使该引脚不存在、也可以通过在属性中设置不同的值来更改开关频率。

后续问题1:

有一份关于系统稳定性的应用报告、我认为这非常有用。

https://www.ti.com/lit/an/slva381b/slva381b.pdf

它解释了带宽和相位裕度的连接及其对系统稳定性的影响。 这些也是快速入门计算器提到的参数。 的确、不仅补偿会影响稳定性、而且反馈电阻器、输出电容和 ESR、电感器和 MOSFET 电阻也会影响。

计算器会将其中的大部分值考虑在内。

后续问题2:

遗憾的是、我在优化 MOSFET 选择方面没有太多经验。 LM5152的数据表中也没有太多有关 FET 选择的文档。 FET 的额定电压必须能够承受最大开关节点电压、同时还为安全留出一定的余量。 此外、低导通电阻值会对效率产生积极影响、也会影响稳定性。

下周我将向大家介绍浮点引脚问题的更新。

如果您同时有任何其他问题、请告诉我。

此致、

Niklas

您好 Niklas、

请参阅以下我的客户回复:

1.如果您的小组主动使用 LM5152-Q1器件为 TI 仿真构建 TINA 或 PSpice、可能会更快。 您可以重新创建"LM5152EVM-BST 用户指南.pdf"中采用的电路(请参阅随附的)。 在我进行有效的仿真后、我可以使电机对 IO 而言是唯一的、

2.补偿器组件(Rcomp、Ccomp、CHF)的确切确定情况如何? 它不像器件规格或其快速入门计算器 Excel 文档显示的那样准确地解释了它们的计算方式。 我猜测外部电压环路会闭合内部电流环路(请参阅随附的"内部外部环路.png"、我刚刚没有看到器件数据表第14或24页中显示的这种双环路系统的实现。

我可能可以解决这一问题、但我想将结果与可能已经解决问题的 TI 专业人士进行双倍检查。

另一个问题、

我想确保方程式11 (10*Rs*IPK =0.6V)

第8.5节将 VCLTH 定义为60mV (标称值)、

将出现第9.2节以说明"峰值 C/L 比较器"、其中 VCS 和 VCLTH 作为输入、

图9-16显示了一个"限流比较器"、其中 VCS 和0.6V 作为输入、

最后,图9-17将 VCS (10*RS*ILpk)与0.6V 进行了比较。

我可能读错了,尽管它看起来似乎等式11是正确的,即10*Rs*IPK = 0.6,但我认为图9-16和9-17标记错误。 0.6V 应替换为0.06V 或 VCLT。

e2e.ti.com/.../8664.Attachment.zip

请告诉我什么是正确的。

此致、

Renan

Renan、您好!

遗憾的是、我们的库仅在当前状态下为 LM5152提供 PSpice 模型。

但是、我认为我发现了浮点引脚误差的来源。 错误消息标记了 IC 的状态引脚、但问题似乎会追溯到 VH_CP 引脚(引脚2)、该引脚在客户模型中连接到 CDither 电容器接地。

对于调试、我建议将此引脚设置为 GND 并禁用其功能。 之后、模型不应再引发收敛错误。

请告诉我、如果客户可以通过这种方式成功解决 PSpice 问题。

我还将查看第二个问题的薪酬计算结果、并在本周结束前返回给您。

此致、

Niklas

您好 Nikals、

请查看我的客户的回复:

请向我发送内部反馈电阻器(FB 分压器-请参阅随附的)的值。

在我获得这些之后、我应该能够完成电压补偿器。

此外、电压补偿器放大器(FB 引脚旁边的放大器)的增益带宽积是多少?

使用 LM5152连接了 TI 项目的当前 PSpice - I 短接"VH_CP"或抖动引脚以越过"STATUS 引脚悬空错误"。

还随附了相应的用于 IO 的 Excel 快速入门计算器。

如何控制启动电感器电流?

我从建议 CSS 值开始、然后递增、尽管我现在看到了变化。 选择 RCS 时、应在约6.77A 的 ILpk 附近启用电流限制、但在所附的图中、ILpk 达到约70安培。

我非常确信我实现了 Excel 快速入门计算器中派生的所有组件

e2e.ti.com/.../Attachment_2800_2_2900_.zip

此致、

Renan

e2e.ti.com/.../1_5F00_LM5152EVM_5F00_BST_5F00_Users_5F00_Guide-PSpice-for-TI.zip

Niklas、

我是这些 LM5152 (升压)问题的相关者(从节点浮动误差开始)。 希望我可以在这个帖子中适应我的当前状态和问题:

1."1_LM5152EVM_BST_USERS_Guide PSpice for TI.zip" 包含用于 TI 瞬态仿真的 PSpice 的当前状态、遵循 TI EVM 板并使用从部件快速入门计算器(随附)派生的部件、

e2e.ti.com/.../LM5152_2D00_Q1_5F00_Excel_5F00_Quickstart_5F00_Calculator_5F00_for_5F00_Boost_5F00_Controller_5F00_Design-8V5.xlsx

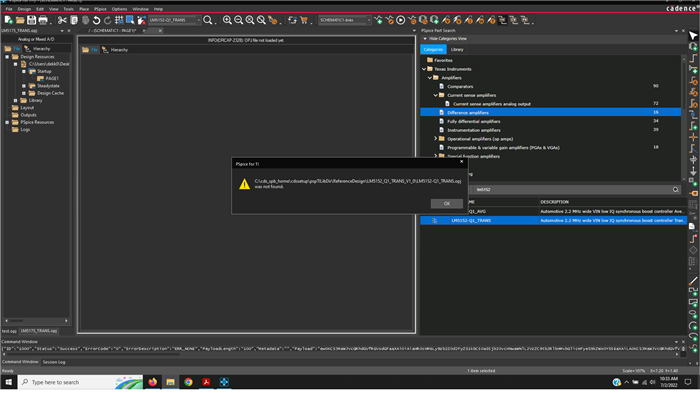

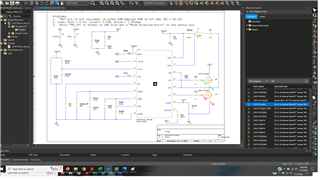

2."Schematic 。png"是 PSpice for TI 原理图的图片、

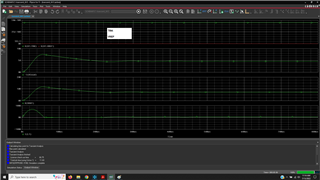

3."Simulation Results.png"是2的仿真结果。 此图的要点是1。 展示输出电压低于预期(设计用于8.5V、可看到大约8.0V 的电压)和2. "VREF"引脚为零伏。 正确设置 TRK 需要 VREF = 1V、因此 VOUT -这里有问题、然后是3。 启动电感器电流会经历较大的浪涌电流。 我希望这个芯片能够解决升压浪涌电流问题。 也许不是。 PSpice for TI 是否具有我可以插入的 NTC 电阻器?

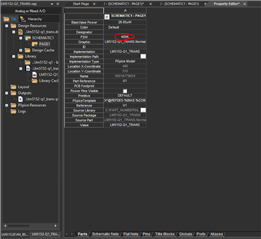

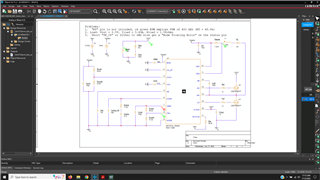

4."Schematic different probes.png"与2类似、尽管 FET 上的探针

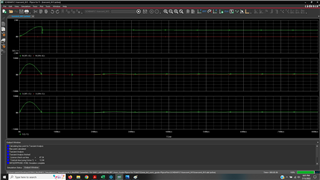

5. "Simulation Results different probes.png"是4的仿真结果。 这张图片的重点是展示没有打开开关、即顶部开关持续打开、底部开关持续关闭。 此 PSpice 模型是瞬态模型还是平均模型???

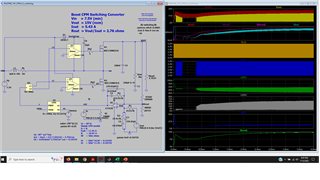

6."3_Boost_CPM_CL_VA_set.png" 旨在演示我知道如何至少通过 CPM 和电压控制(内部/外部控制环路)设置升压开关转换器的 LTSpice 仿真 我知道如何正确设置其相应的小信号模型以构建尺寸合适的补偿器组件、即我知道我在做什么。

7.我知道该器件采用 OTA II 型电压补偿器、但我不相信该 OTA 提供了增益(提供了电流感应放大器的增益、10V/V)或其电阻分压器值(请参阅 TI "slva662.pdf")。 我应该能够设计电路的闭环增益并对其进行建模、如果给定这些值、则推导 Rcomp、Ccomp 和 CHF。

优先级:

1. 我认为部件 PSpice 模型有问题-见上文1-5。 在我建议购买之前、我非常希望此仿真能够正常工作。 如果您同意该模型存在问题(我很可能设置了错误-我确实犯了错误)、并且如果同意、TI 可能会使该模型正常工作、请告诉我。

2. 我想知道 OTA II 型电阻分压器的值和增益-请参阅上面的7、

3. 我还想知道 TI 如何衍生 Rcomp、Ccomp 和 CHF。 TI 的某个人必须在某个位置拥有此信息。 我为我的仿真推导出了这些值(请参阅上面的6)。 我猜、如果我拥有所有信息、我可以对该部分执行相同的操作。

对于信息转储和问题、我深表歉意。

谢谢、

Craig

Craig 和 Renan、您好!

我让 Niklas 回答 PSpice 问题。

但关于补偿问题,我需要在这里发言。

为了计算外部组件、TI 创建了 Excel 快速入门计算器。

我们很高兴拥有了这款工具、我们的内部工程师也依靠它。

这些方程受到保护 、因为它们使用的一些参数被视为 TI 意图信息。

请在快速入门计算器中输入功率级参数、以根据您选择的组件计算补偿网络的三个组件。

(在 TI 内部、我们将完全相同。)

显示器件内部信息的图并不是可用于计算的准确原理图。

它们只是为了说明我们内部正在发生的基本原则。

在本例中、它旨在显示实际反馈分压器位于器件内部、以及如何改用 TRK 引脚。

同样、确切的详细信息被视为 TI 意向信息、不会打开。

您所要求的参数对于操作零件不是必需的、因此不是公开的。

即使您已经安装了这些器件、我也无法保证内部电路的图是否完整、或者误差放大器周围是否存在其他组件、但这些组件并未显示出来。

此致、

哈里

您好 Craig、您好 Renan、

我将详细了解您的设计和 LM5152、以查找此问题的根源。

我将在下周中旬回到这里、了解更多详细信息。

关于第3点。)

如果 PSpice for TI 库不包含所需的器件、则可以实现第三方模型。 唯一的缺点是、之后只能同时放置三个仿真探针。

有关如何包含附加模型的指南、请访问:

training.ti.com/pspice-ti-3rd-party-model-import

关于第5点。)

模型零件的描述表明它是瞬态模型还是平均模型。

LM5152_TRANS 在这种情况下意味着它应该是瞬态模型。

此致、

Niklas

您好、Craig、

我对您的模型进行了一些仿真、并看到了相同的行为。

由于器件未切换、我的第一个假设是器件永远不会启动并保持关断模式。

查看 UVLO/EN 引脚时、我注意到反馈分压器(RuvIotb)上的下电阻仅为8欧姆、而上电阻为36千欧。 因此、UVLO/EN 引脚上的电压低于启动阈值。

我将 UVLO 引脚连接到 VSUPPLY、以确保器件在所有情况下启动。 之后、IC 开始开关、输出电压达到所需的8.5V。

我建议也从您的一侧检查 UVLO 引脚上的电压、并查看是否可以进行更改以启动器件。

如果您能取得进展或有其他问题、请告诉我。

此致、

Niklas

Niklas、

很棒的地方!

我向该电阻器添加了一个"K"、但我仍然看不到开关。

VUVLO (引脚)大约为2V、开关不会启动。 将底部电阻器增加到20k (VUVLO = 2.5V)、但它仍然没有开始开关。

问题1:

VUVLO 阈值到底是什么? VUVLO 阈值是否约为1.2V? 我将查看这里的上升阈值电压。 这种价值对我来说并不明显。

将 VUVLO 引脚连接到 VSUPPLY 可实现电路切换。

问题2:

是否有充分的理由不将 VSUPPLY 直接连接到 UVLO/EN 引脚? 根据数据表原理图、该引脚似乎不能灌入大量电流。 只需遵循数据表和快速入门计算器即可。

我正在讨论问题3 (涉及补偿器组件)、

谢谢、

Craig

Niklas、

问题3 (我上一组问题的后续问题)。

Harry 提出了向用户提供部件内部电流和外部电压环路完整详细信息的想法。

PRO: 快速入门计算器允许设计/验证单个工作点(Vsupply = fixed1、Iout = fixed1)、

Con: 快速入门计算器不允许验证特定的补偿器设计是否在整个工作点范围(Vsupply = Vmin/Vmax、Iout = IMIN/Imax)下工作。

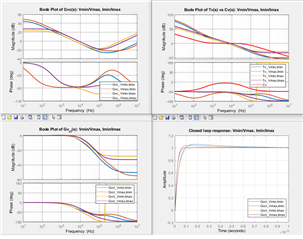

请参阅随附图片:

在给定完整工作点范围(Vmin/Vmax、IMIN/Imax)的情况下、左上角的图是 vcontrol 到 Vout (CPM 简单近似模型的 GVC)的波特图、

在使用 II 型电压环路补偿器闭合 GVC 后的环路增益波特图、给定针对电压环路补偿器传递函数的频率响应的完整工作点范围(深红色)、

底部的图绘制 了相应的闭环频率和阶跃响应、同样给出了完整的工作点范围。

现在、我使用部件 PSpice 模型、我可以验证系统在整个工作点范围内是否稳定、但仿真需要很长时间、 但是、如果任何工作点不稳定、我需要即插即用(在快速入门指南更新的情况下)、直到达到所有工作点、这会显著增加我必须专门用于此部件的时间。

请重新考虑让用户完全接触零件内部和外部环。

谢谢、

Craig

您好、Craig、

我很高兴听到您的模型正在运行。

正确、UVLO 的阈值应约为1.2V。 因此、在该 PSpice 模型中、UVLO 引脚的电压需要更高、这也使我感到困惑。

关于您的第二个问题、我同意在将 UVLO 直接连接到 VSUPPLY 时不应有任何缺点。 如果需要在定制电压下触发欠压、分压器只是一个功能。

Q3)很抱歉 、快速启动工具同时仅显示一种操作情况、给您带来不便。 我们不断尝试 改进产品支持的设计工具和资源、因此非常感谢您的反馈。

很难完全访问详细的设计结构、因为这些数据通常包含机密数据、因此我希望您了解到、我们无法提供所有 TI 器件的完整设计详细信息。

Q4)查看原理图时、我假设并非所有浪涌电流都流经 FET。 输入和输出电容器的初始充电需要大量电流。

我建议尝试使用电容器初始条件(IC)进行仿真、以设置其所需的工作电压、并检查电感器、二极管和 MOSFET 的电流以及软启动行为。

此致、

Niklas

Niklas、

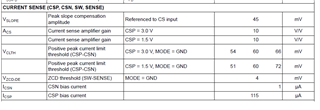

具体如何确定给定 CSP (3.0V 与1.5V、给定模式= GND)的 VCLTH 工作/制造范围?

MODE = GND 只应用于"固定"跳过模式。 我计划使用 FPWM、即连接到 VCC 的模式、

我不知道如何确定 CSP 3.0 vs 1.5V 部分。 到目前为止、我的最坏情况峰值电感器电流约为12.7A、RS 为4mohms、因此 VCSP = 0.0508V。

不确定我是否应该假设 VCLTH 范围为54至66mV 或51至72mV。

请告诉我在我的设置下应该使用的范围。

谢谢、

Craig

Niklas、

为避免此部件出现收敛错误、最佳设置是什么?

我正在使用快速入门指南中的部件。

我将仿真容差值保留为标准值。 通常、如果我遇到收敛错误并放宽容差、结果将变为无用。

无论是否存在电容器谐振器、我都会得到收敛误差。

我在没有单步执行输出的情况下获得收敛错误。

如果我将输入电压从最小值更改为最大值(根据快速入门指南)、则会出现收敛错误。

我真的无法判断我是否有器件问题、快速启动补偿器问题或 TI 的 PSpice 问题。

我已经旋转了几天的轮子、试图获得一个相当好的仿真结果。

谢谢、

Craig

Niklas、

我附加了一个示例、其中控制器大约需要2.5ms 的时间开启或至少开始开关。

有什么想法吗?

谢谢、

Craig

Niklas、

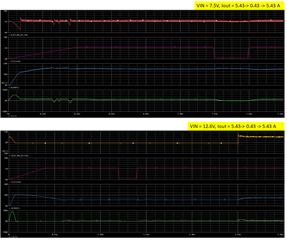

后续仿真结果。

顶部图片、Vin=7.5V、似乎工作正常。

底部图片、Vin = 12.6V、导通(开关)延迟很长。

此外、器件数据表的第6页列出了最大 HB 转 SW 为5.8V。 该页面的注3表示在超过5V 的电压下工作时、预期寿命可能会降低。

每张图的顶部图显示了 HB 转 SW。 如果不等于5.8V、则两条迹线看起来都大于5.8V。

HB 到 SW 限制写入正确还是仿真错误或其他问题?

谢谢、

Craig

您好、Craig、

感谢您发送更多详细信息。

关于 PSpice 收敛问题:

一般而言,往往很难找到趋同问题的根源。

我检查了您最近的原理图、找不到任何明显的连接问题、尤其是因为该设计以 EVM 参考模型为导向。

我注意到、您使用特定的模型器件替换了 MOSFET。 您是否知道在选择这些部件后收敛问题是否增加?

在这种情况下、我建议在调试阶段保留 PSpice for TI 库中的理想 FET。

增加的 HB 和 SW 引脚电压差也可能与 FET 有关。

根据数据表、当输出电压高于过压阈值时、STATUS 引脚的下拉电阻器会打开。

在器件完成启动之前、似乎触发了阈值、但一旦器件开始运行、状态引脚电压会降至零。 我假设、这可能是仿真开始时的输出电压尖峰导致的。

此致、

Niklas

Niklas、

理想的开关:TI 不提供"参考模型"(请参阅上面您的第一个答案)、因此我只处理我构建的项目、而我只使用真实的开关。

为了澄清这一点、LM5252站点不包含完整的仿真、即 LM5152、与 LM5152 PSpice 模型相比、LM5152已将各种组件设置为提供特定的输出电压。

如果存在"完整仿真"、请告知我。

2. HB 转 SW 引脚: 是否有任何方法可以确切地了解 HB 转 SW 引脚的工作情况? 这可能归结为此控制器的推荐 FET。 我目前正在使用 TI FET CSD17581Q3A、因为它在库中可用、但我计划使用与 TI 器件 BUK9Y12-40E 类似的 AEC 级器件。 至少我想获得一个 TI 推荐的 FET、它不会导致 HB 到 SW 的违反、假定这是一个真正的问题。

我认为这两个 FET 都适合此引脚/应用。 如果我错了、请告诉我、并/或推荐更好的产品。

STATUS 引脚:这是 TI 模型的 PSpice 问题还是我做了一些错误? 我想我看不到您所指的电压尖峰。

一般而言、我想知道我是查看 PSpice 模型错误还是我的行为上的设置错误。

谢谢、

Craig

Niklas、

此外、栅极电阻 RGLOW 和 RGHIGH 是如何确定的?

我知道、如果在部件组装后开关切换至 FAST、通常会增加栅极电阻。

此外、添加了栅极电阻以限制来自栅极驱动源的电流、尽管我认为该器件上的栅极驱动是限流的(在这里可能是错误的)。

也许高侧自举能够为高侧驱动器提供拉电流的可能性。

我可以理解 为什么将 RGLOW 设置为零。

为什么 RGHIGH 设置为2欧姆?

谢谢、

Craig

您好、Craig、

我们为 LM5152-Q1器件提供了完整的仿真模型、这可能会进一步帮助您。

e2e.ti.com/.../LM5152_2D00_Q1TransientModel.zip

这将对输入电压为5V、输出电压为10A、输出电流为5A 的升压转换器进行建模、并使用简化的开关来替换 FET。

此模型显示 HB - SW 电压差或 STATUS 引脚没有问题。 因此、可以将此模型作为基础并开始根据所需的自定义参数进行调整。

您还可以使用模型中更真实的开关替换开关、并检查 HB 到 SW 的电压问题是否 再次出现。

此致、

Niklas

Niklas、

如何使用此规格估算 RG (FET 栅极电阻器)?

指定了高/低/拉/灌电流;但是、不指定高/低/拉/灌电阻。

通常、我使用以下类似的方法:

I_SOURCE =(VCC - VGS_TH)/(R_SOURCE + RG)、然后求解 RG、其中 VGS_TH 是 FET 阈值 VGS 电压。

假设 R_source 为零还是"压降"/源?

谢谢、

Craig

Stefan、

您是否暗示驱动器拉电阻/灌电阻的标称值如下所示:

R_SINK_H = 0.08/0.1 = 0.8欧姆

R_SOURCE _H = 0.04/0.1 = 0.4欧姆

R_SINK_L = 0.08/0.1 = 0.8欧姆

R_SOURCE _L = 0.04/0.1 = 0.4欧姆

其中 I_Source/I_Sink = 100mA

因此、栅极电流 IG 应该为:

IG_SOURCE _L = 100mA =(VCC - VGSth)/(R_SOURCE _L - RG)

其中 VGSth 是 FET VGS 阈值电压、RG 是栅极电阻、需要求解。

我需要在这里得到详细的答复。

谢谢、

Craig

哈里

关于 LM5152器件的数据表...

问题重新启动....

我想根据器件数据表中的参数和近似电路模型来预测外部 FET 栅极电阻:

一种可能的低侧拉电流电路模型:

(VCC-VGSth)/(Rx + RG_LOW)= IG

其中:

VCC 范围为4.75V 至5.25V (请参阅规格的第8页)、

在我的例子中、VGSth 是 FET 的 VGS 阈值电压、范围为1.4V、1.7V、2.1V (最小值、 标称值、最大值)、

RX 是 PWM 驱动器的输出电阻。 当驱动器拉取栅极的 FET (导通)或灌入栅极的 FET (关断)时、可能不同、也可能不同。 当打开时、我将其命名为 Rsource、当关闭时、我将其命名为 Rsink、

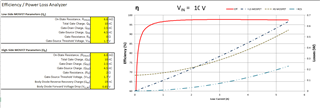

IG 是驱动器栅极电流。 根据数据表第10页的定义、IG 似乎被限制在100mA 灌电流和拉电流(请见所附图片)、

RG_LOW 是我所需的低侧 FET 外部栅极电阻。

来源:

IG =(VCC - VGSth)/(Rsource + RG_LOW1)

求解 RG_low1:

RG_LOW1 =(VCC - VGSh - IG*拉电流)/IG

灌电流:

IG =(VGSth)/(Rsink + RG_low2)

求解 RG_low2:

RG_low2 =(VGSh - IG*拉电流)/IG

对于高侧、数学应该非常相似。

问题:

我不知道 Rx (Rsource/Rsink)、

数据表中似乎未具体指定该值、

我不清楚到底是如何得出这个/这些值的。

也许我完全不了解该规格、完全错过了 Rsource/Rsink 和/或 RG 值。

Harry -在上面、您提出了以下建议:

"建议使用 1.0 / 1.5 / 1.7欧姆的最大值、以确保 FET 在最坏情况下能够正确导通。"

但是、您不能指定是指 Rsource/Rsink 还是 RG 值。

然后您进行以下澄清:

" 数据表第10页中的最大值、而不是典型值。"

但是、我在数据表第10页的任何位置都找不到这些值。

请务必详细说明您的回答!

问题:

具体如何确定此部件的 RG (高电平和低电平)?

请准确列出您从数据表中提取的值(以及在何处)以及所采用的模型和近似值。

写出步骤/数学对我来说很有用。

我知道在组装电路后可以/应该调整 RG、但我真的想能够预先预测这些值。

谢谢、

Craig

您好 Craig、

当您说"明显不同"时、我不知道您正在查看哪些组件。

我假设您正在查看我们的 EVM。

正如我在另一个线程中提到的:这些组件充当到器件输入端的"接线"端接、以提高抗噪性能。 其值取决于 PCB 参数。

您基本上可以在此处比较的 EVM 的所有感应线路中找到100欧姆电阻器。 更改这些电阻器(或移除其中一个电阻器)将有助于调整输入引脚上的信号。

当您比较用于快速内部电流环路的感应输入的电容器时、这是100pF 与47pF。 这没什么影响。

这些电容器必须保持相当小的尺寸、以避免内部控制环路失真。

外部平均电流环路要慢得多。

0.33µF、LM5176 VOSNS 引脚上的电容可选择大得多的电容(μ F)、以平均更大的失真。

没有一个用于一切的方程。 这些组件的值取决于 PCB 参数。

提前尝试和计算这些值毫无意义。 现实无论如何都是不同的。

当我们设计新的 EVM 时、我们转到实验室、测量哪些值最合适。 (未使用方程式)。

一般情况下:

即使您的 PSpice 仿真将为您提供完美的结果、您也会发现实际电路板的工作方式与仿真显示的不同。

此外、当两个人设计具有完全相同组件的相同应用的电路板时、他们会获得非常不同的结果。

这只是因为组件的不同放置方式以及 PCB 上的不同布线。 仿真不会涵盖许多副作用和寄生效应。

此致、

哈里