主题中讨论的其他器件: LM5106、 TINA-TI、 LM5109B

大家好、

当 VDD 为0V 和0~9V (低于建议运行条件)时、我有一个有关 LM5102 HO/LO 状态的简单问题。

高阻态、上拉、下拉?

不过、我认为0~9V 是未知状态。

此致、

Kai

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Nomiyama-San、您好!

该驱动器具有称为 UVLO 的功能、如该表所示。

这在驱动程序中的工作方式如下:

看到馈入与门的 UVLO 块? 与门为低电平意味着驱动器将处于下拉状态。 UVLO 还具有迟滞功能、因此确切的阈值会因 VDD 上的上升或下降而异。 假设一切都是典型值、对于下降、从9V 到6.4V (6.9V - 0.5V 迟滞)、驱动器应继续运行。 上拉或下拉 将由输入决定。 在此下方、无论输入如何、驱动器都将被下拉。 但是、一旦 VDD 足够低(未测量确切阈值)、偏置就不足以使 IC 正常工作、并且模块停止正常工作。 这会导致输出上出现某种高阻态/未知状态、但由于 ESD 二极管和体二极管、它可能不会具有很高的阻抗。 希望这对您有所帮助。

谢谢、

Alex M.

您好 Kai、

因此、10-20k Ω 之间的任何位置通常是安全的选择。 电流消耗将约为 VDD/Rpulldown、因此在10k 时、导通时的电流消耗约为1.2mA、20k 时的电流消耗为0.6mA。 但是、在如此低的工作频率下、您应该小心处理自举电压。 下面是一些快速计算:

I = C * dV/dt & I = VDD (12V)/RPD

12/RPD = Cboot *(ΔV μ C/Ton (500us))

ΔV = 0.006/(PD*Cboot)

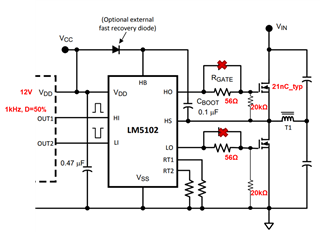

我提出这个问题的原因是、10k 下拉电阻和100nF 自举电容意味着在您运行时 HO 会下降大约6V。 下面是一个显示了这一点的仿真:

您使用的是什么自举电容? 更大的电容应该有助于减少这一问题、尤其是因为您的工作频率如此低。 如果您想对此进行仿真、可以使用 LM5106模型。 它们具有极其相似的功能。

总之、Vgs 下拉电阻器很好、但请确保它不会给高侧自举电路带来问题。

谢谢、

Alex M.

尊敬的 Alex:

我总结了随附的 Excel 文件中的每个参数以满足客户需求。

计算得出的 Cboot 值为5nF、客户使用1uF 作为 Cboot。

我尝试使用 LM5106模型进行仿真、但由于错误、无法进行仿真。

我使用随附的 TINA-TI 估算20kohm PD。 HB 最小电压看起来是8.65V (9Vmin-350mV※二极管 Vf=750mV、因此添加350mV、因为 Vdh=1.1Vmax)> 6.7V (VHBR-VHBH)、但您能否再次检查以下配置是否正常?

此外、数据表中提到了以下内容、但图16 VDD 旁路电容器为0.47uF、比0.1uF CBoot 的电容不大10倍。

该要求中应使用的是拼写错误还是 Vdd 旁路电容值?

"通常情况下、本地 VDD 旁路电容器应比 CBOOT 的值大10倍。"

e2e.ti.com/.../LM5102_5F00_Boot_5F00_Strap.TSC

此致、

Kai

您好 Kai、

配置看起来不错。 您是否打算在设计中使用外部自举二极管? 可能没有必要。 我还遇到了 LM5106模型的问题、但使用 LM5109B 模型(稍微接近)时、我能够对其进行仿真、结果接近于我的预测。 由于下拉、您可能会在一个周期内看到 HO 上大约0.5V 的压降、这不是很大的压降。 使用大型自举时、自举电容器可能需要几个周期才能充电至 VCC-VFD、但一旦达到稳定状态、就可以了。

VDD 旁路电容器>10x Cboot 只是建议在 Cboot 充电时防止 VDD 下降太多。 这个图表很可能是在我们采纳该建议之前制作的、并且从未更新过。 我建议遵循10X Cboot 建议、但请确保 VDD 旁路至少大于 Cboot。 此外、我们倾向于建议并联一个更小的 VDD 旁路电容(100nF 左右)、以便更好地滤除高频噪声。

谢谢、

Alex M.