您好!

我们目前正在应用中使用 UCC21750驱动器(三相逆变器400V 10kW)。

在某些情况下(在分析中)、驱动器会在大约1ms 内停止 PWM。

这种行为似乎类似于激活内部欠压查找或激活短路保护。

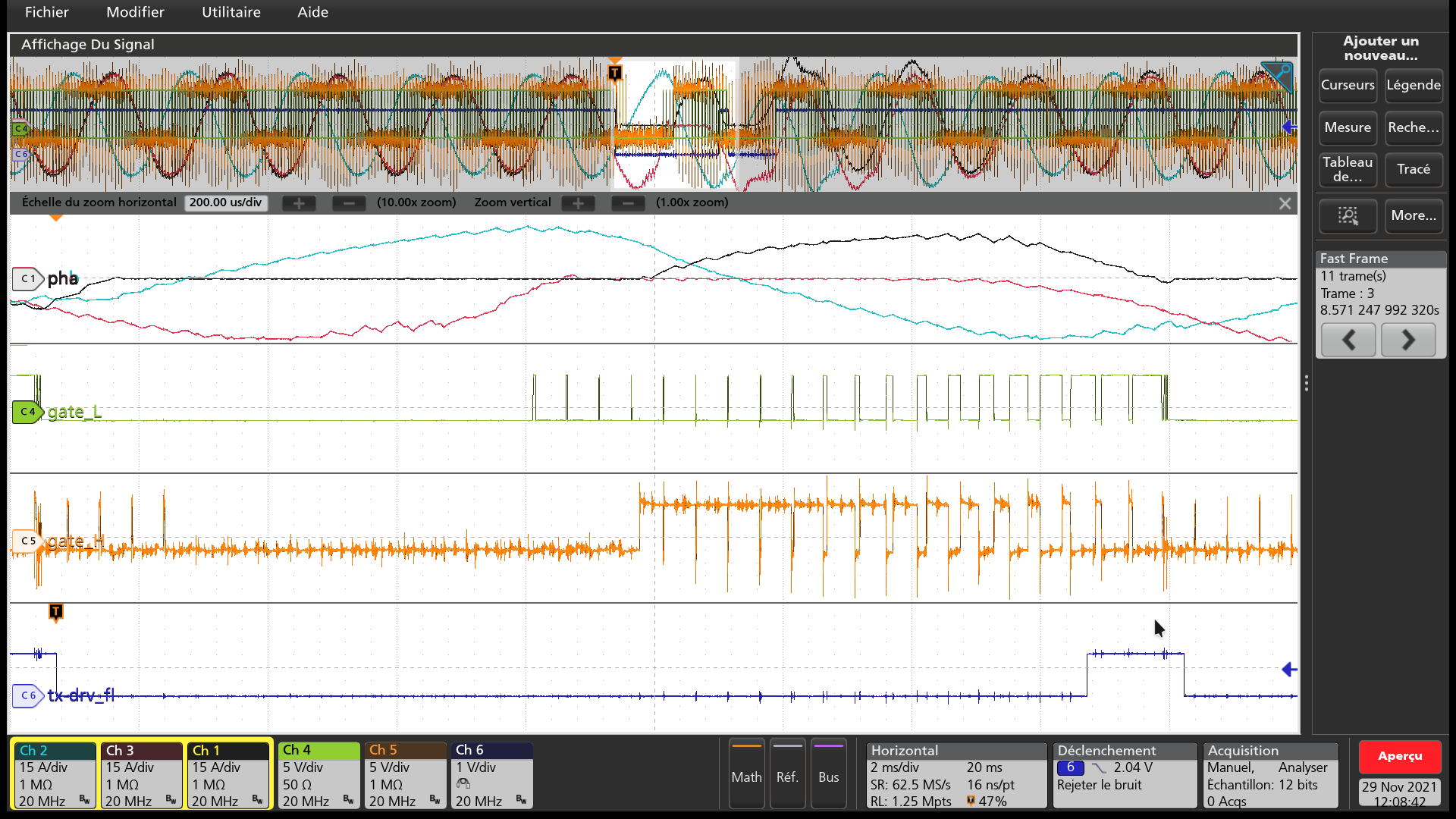

C4 :带有高抑制差分探头的栅极电压

C5 :带差分探头的栅极电压

C6:所有驱动器的 DRV 标志,具有附加监控功能

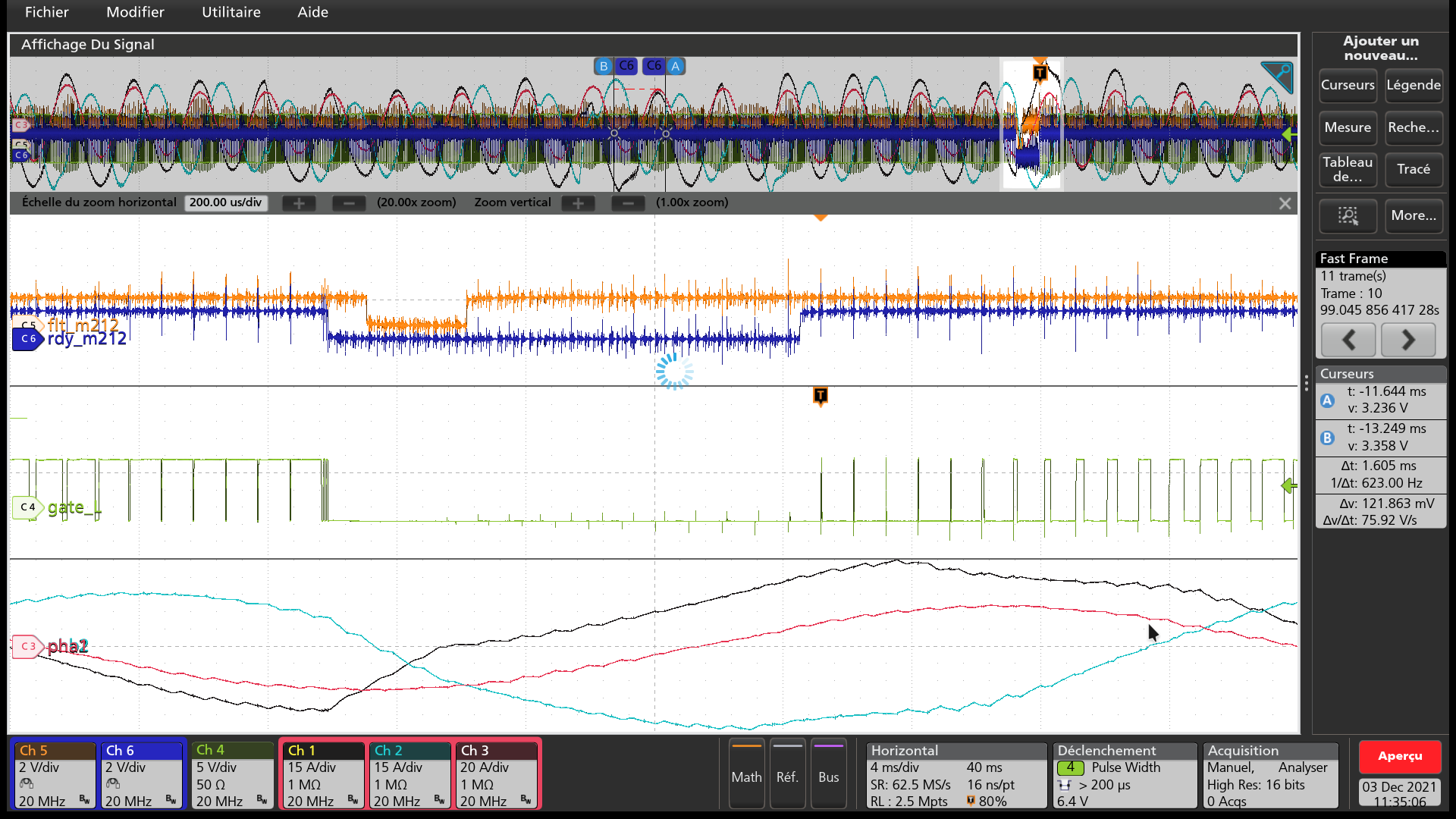

C4 :带有高抑制差分探头的栅极电压

C5 : UCC21750的 FLT 标志

C6: UCC21750的 RDY 标志

当‘器停止时,我们会在驱动器的“长停止”(tFLTMUTE 或 tRDYHLD)之前观察到栅极电压上有一个额外的脉冲。

您是否有什么想法会导致这种行为?

C5和 C6 :驱动器的 PMW_H 和 PMW_L 输入

C4 :带有高抑制差分探头的栅极电压

另一个问题是、在 VCC=3、3V 和 VDD=15V 时发出 RDY 标志

您是否有什么想法会导致这种行为?

非常感谢您的支持。