如何防止在加电期间功率 FET 误导通?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

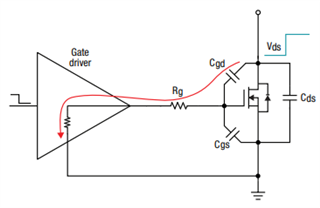

在栅漏极电容与栅源极电容相比较高并且在上电期间出现高 dv/dt 的应用中、通过栅漏极电容器的电流有可能导致功率 FET 误导通。 通常情况下、内部驱动器钳位可防止这种情况发生、但在条件特别严重的系统中、此电流会突破内部驱动器钳位的限制、甚至导致误导通。 虽然这在大多数电路中不是问题、但在某些情况下、例如当功率晶体管具有非常大的 CGD 时、需要使用外部钳位电路。

当栅极驱动器首次上电时、开关节点电压通常已经发生变化、这通常是因为低侧晶体管已经在开关。 开关节点电压的这种变化会转化为高侧功率晶体管上的快速 dVdt、从而导致电流流经晶体管的米勒电容器 CGD。 如图所示 当米勒电容与 CGS 之比较大时、该电流需要另一条路径、流经栅极电阻并流入驱动器。 这会导致 Rgate 两端和驱动器内部的电压差、从而可能使栅极电压升高到足以打开功率晶体管。 虽然驱动器通常具有内部钳位电路来防止这种误导通、但功率晶体管上具有高 dVdt 或具有大米勒电容的系统可能会产生过大的电流供内部钳位处理。

图 1:寄生电容

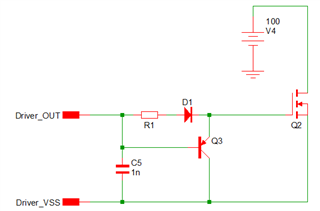

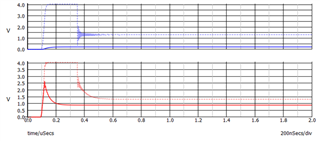

为了防止这种误导通的可能性、可以实现外部钳位电路、如 图所示 该电路添加了一个二极管和 BJT、以便在驱动器关断时提供强下拉电阻、从而钳制任何可能在其他情况下打开功率晶体管的电流。 此钳位的影响如图 3所示、蓝色波形显示 Driver_OUT 电压、红色波形显示 Q2栅极电压。 虚线没有 Q3钳位电路、实线有额外的钳位。

图2.

图3.