简介

通常、大多数 IC 采用 SOIC 和 DFN 等行业标准封装。 即使在竞争对手中、许多器件都设计为具有相同的引脚排列、因此可以轻松更换或升级。 去年出现了供应问题、导致人们对将旧器件用作临时替代器件的兴趣增加。 其中一个问题是、旧器件可能无法与新器件的性能相匹配。 但是、设计人员可以采取一些措施来适应这些性能差异。

调整驱动强度

较新的器件往往具有较高的峰值拉电流和灌电流。 其优势在于它可以降低 FET 中的开关损耗、这对于在较高频率下运行尤其重要。 缺点是高电流会导致 FET 栅极上的噪声和振铃、尤其是在布线和布局不理想的情况下。

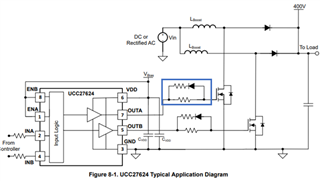

蓝色框显示了栅极电阻的常见布局。 反并联二极管和电阻器允许单独配置峰值拉电流和灌电流。 强烈建议在设计系统时为栅极电阻器设置占位符、以便可以尝试不同的电阻值。 当选择具有不同拉电流/灌电流的新驱动器时、请增大栅极电阻以减小峰值电流、或减小栅极电阻以增大峰值电流。 这些文档提供了有关调整峰值拉电流和灌电流的其他信息。

散热和开关

DDA 和 D 等一些封装可以相互引脚对引脚替代。 DDA 封装只是一种带有散热焊盘的 D 封装、可改善散热。 如果从 D 封装切换到 DDA 封装、热性能会提高。 但是,如果散热焊盘未连接到接地层,则 D 封装的性能将不会有很大改善。 如果从 DDA 切换到 D、则应检查热性能以确保 IC 不会过热。

该公式给出了驱动器中耗散的功率近似值。 将 PQG 乘以所选封装的结至环境热阻(RΘJA)将粗略估算器件将经历的温度升高。 有关详细信息,请参阅器件数据表的“详细设计过程”部分。 UCC27289数据表第18页的第8.2.2.3节特别详细说明了这一点。 应该注意的是、这些公式是估算值、布局等其他因素会影响热性能。 请参阅以下有关 IC 热性能的文档:

CMOS 与 TTL

这些逻辑架构决定了输入引脚上产生高电平或低电平输出的电压电平。 只要控制器能够驱动输入超过数据表中描述的阈值电压、输入就会进行寄存。

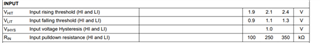

例如、UCC27289具有 TTL 输入、但也可以接受 CMOS 类型的控制信号。 只需参考数据表的电气特性输入部分:

在这种情况下,只要输入信号的高电平超过2.4V,低电平低于0.9V,输入就应正确注册。

仅半桥

自举电路

一些驱动器包含内置自举二极管、而其他驱动器不包含自举二极管。 内部二极管可减少电路板的器件数量、但可降低设计灵活性。 如果系统中先前的驱动器具有外部自举电路、则可以直接插入具有内部二极管的驱动器作为替代。 外部自举电路可保持未组装状态以断开电路。 然而、反向情况–使用不带二极管的驱动器替换具有集成二极管的驱动器-需要重新设计以添加自举电路。 请参阅以下有关自举电路的文档:

HS 噪声

由于电感负载的快速切换、许多应用、尤其是电机、可能会产生较大的电感电压尖峰。 该噪声将出现在驱动器的 HS 引脚上、如果幅度足够大、可能会导致损坏或性能问题。 所有驱动器在 HS 引脚上都有一定数量的负电压、它们可以毫无问题地加以处理、这将显示在数据表中。 但是、如果噪声对驱动器来说太大、则必须采取其他步骤来降低噪声。

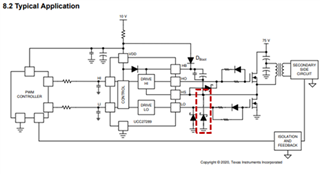

红色虚线框显示了放置在 HS 引脚附近的肖特基二极管、这是降低噪声的常用方法。 如果噪声尖峰超过二极管的正向电压,二极管将导通并将 HS 拉向接地。 理想情况下,这会将负 HS 电压限制为二极管的正向电压。 同样、可在 LO 和 HO 引脚上使用肖特基二极管以相同的方式降低噪声。

使用的另一种方法是缓冲电阻器。 在驱动器的 HS 引脚和负载之间放置一个小电阻器可以降低 HS 上出现的噪声幅度。 缺点是该电阻器位于自举的充电路径中,因此它取代了 Rboot 电阻器并限制了充电速度。

最后、布局是降低此类噪声的重要工具。 HS 平面应较大、但应尽量减少与其他平面和布线的重叠。 此外、建议将信号接地平面和电源接地平面分开、以防止输出上的接地噪声导致输入信号出现问题。