主题中讨论的其他器件:UCC21710、 UCC21732、 UCC25800、 SN6505B

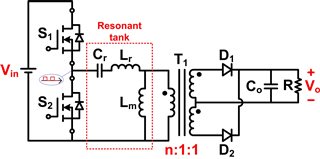

对于由 Moog Inc 赞助的项目、我们将设计一个5kW、1MHz 双向 CLLC 谐振转换器。 对于初级侧、我们使用650V SiC (在 SEMI NVH4L015N065SC1上)、我们想知道您是否有推荐的或合适的栅极驱动器来在1MHz 下开关此类器件

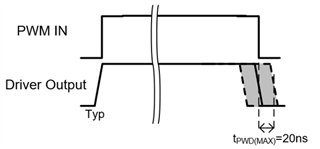

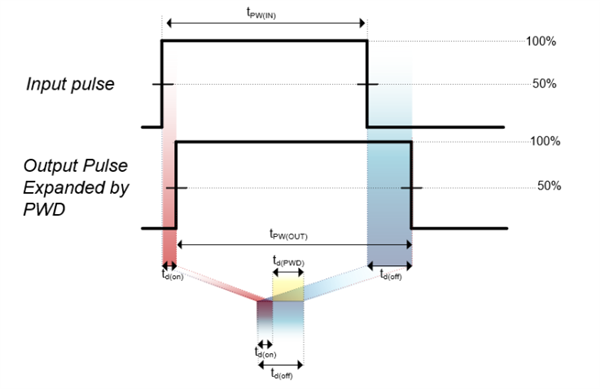

在浏览您的隔离式栅极驱动器选项后、我注意到所有这些选项都具有建议的最大开关频率为1MHz。 哪些因素决定了该限制? 它是否在驱动器电气内部、是否由于散热问题等