主题中讨论的其他器件:LM5121、 LM2766

我想将断开 FET 用作输入电容的浪涌限制器。 这意味着 FET 将位于输入电容器和 Vin/CSCP 连接之前。 这是否起作用、是否可以使其工作(使用附加电路)?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

感谢您的快速响应。 我应该在描述中更加清楚。

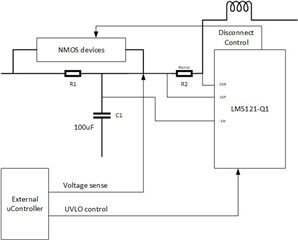

我打算放置一个串联电阻器来为输入电容器预充电、因此 IC 实际上会通电、但不会运行、因为 UVLO 将保持待机状态。 将会有一个外部 uC 来监控许多电压和电流、因此 uC 将知道输入电容器已充电。 IC 将通电、但不消耗太多电流、因此预充电电阻器上的压降不会 产生太大的压降。 我在数据表中看到的图37和38使用 DG 和 DS 引脚来支持用于反向电池保护的外部 FET。 我最初没有考虑过电池反向保护、但这是一个有趣的补充。 可以使用附加的 NMOS 器件来增强图38、以提供电池反向保护功能和浪涌限制器旁路功能。 R1允许输入电容器以合理的速率(100至500欧姆电阻器)充电。 然后、当5121准备好激活时、FET 将绕过电阻器、并使用大约5至10m Ω 的导通电阻将电容连接到输入端。 当 FET 导通时、电阻器上几乎没有电压。 我意识到,当激活“断开功能”时,R1仍会为 IC 提供一些电源,但通过外部 UVLO 控制,该器件可以处于待机或关断状态。 该概念的方框图如下所示。 这是否可以使用图 38作为起点?

Dan、您好!

这是一个有趣的想法。 图38本身不能用作浪涌限制器、因为其体二极管指向负载侧。 您的 R1将被体二极管绕过。 但是、如果您翻转 NMOS、则它可能与 R1一起用作浪涌电流限制、但请注意、您会失去反极性保护(因为体二极管指向输入源)。 无论如何、我们尚未测试过这样的浪涌限制器电路、但我认为您可以 通过测试来验证功能。 实验始终是必要的步骤。

谢谢、

Youhao

我无法使浪涌/极性保护电路正常工作。 我意识到我需要添加一个与源极串联的二极管(如绿点所示)、以防止栅极-源极结击破(最大20V)。 我已经验证过、如果我从5121上断开电源并提供一个外部电源来提供-10V 偏置(Vgs)、那么电路将正常工作。 我可以通过控制 P-MOS FET 来打开和关闭两个 N-MOS FET。 但是、即使电源从5121断开、电荷泵也不会为电源提供正电压。 我测量的电压比 Vin 低大约8伏、我预计它至少比 Vin 高10V。 我已将一个100pF 电容从 DG 连接到 DS、并将一个499K 电阻从 DS 连接到接地、如该规范的图38所示。 我使用 UVLO 功能来管理浪涌状态。 我将 UVLO 拉至接地以将5121置于关断模式、而浪涌电路允许输入电容器通过极性保护二极管和499欧姆电阻器进行充电。 当系统准备好启动5121时、将移除接地端以允许转换器启动。 (至少这是计划) 、但电荷泵没有达到我认为的效果。 您能看到我出了什么问题吗?

谢谢。

德传、 我将检查启动顺序、但我使用电压表进行了测量、可以验证 UVLO 电压是否超过1.2V、VCC 是否导通。 今天、我将尝试获取该序列的一些示波器曲线、并对此进行更新。 我已附上该设计的原理图供您参考。 这是一个测试板、因此序列由我施加外部电压(45至50V)并将 P2接头接地开始。 我已将二极管 D5替换为短路 、以便 UVLO 状态为关断而不是待机。 这样消耗的功率更少。 我可以看到、输入电容器充电至接近输入电压的电压。 R18电阻器会降低一些电压、因为 LM5121在关断时消耗一些电流。 然后、我打开 P2上的接地连接、以允许转换器启动。 我可以看到、输入电流增大、VCC 打开、但 FET 不会打开 OH、输入电容器上的电压降低、因为增大的电流仍会流经 R18电阻器。

对原理图中显示的值进行了一些更改。 R23现在为20K、以将 UVLO 阈值更改为30V、R22现在为10K、C12现在为0.033uF、连接到 C5的电阻器更改为499K (在初始设计期间输入值时的误差)。 我已经验证了基本转换器的工作原理。 我短接了浪涌 FET 并移除了 P-MOS FET Q3并验证了基本设计。 (P1接地以提供正确的开关频率)

正如承诺的那样、这里是启动序列的一些图。 但愿这对您有所帮助。