主题中讨论的其他器件: TPS546D24A、 TPS546A24A

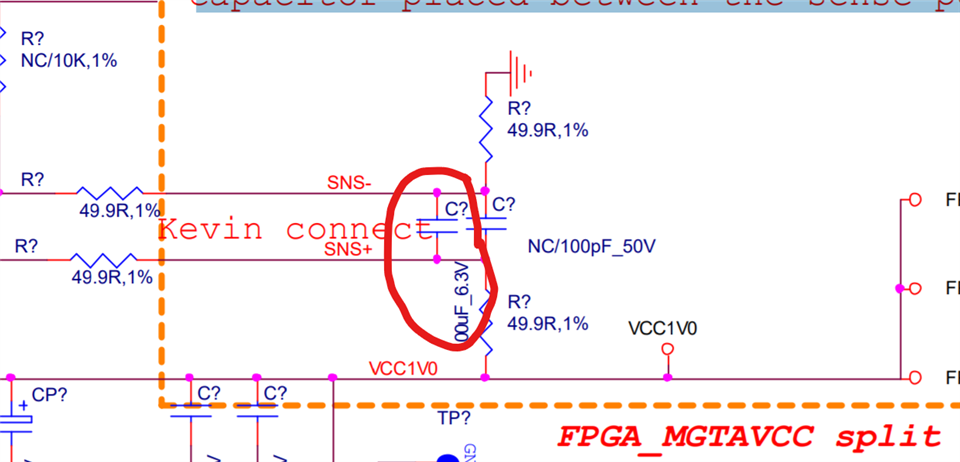

您好,我使用 TPS546B24A 作为 FPGA 内核电压电源, ‘、但 TPS546B24A 似乎无法正常工作。在我 将引脚27 (EN/UVLO)设置为高电平后、引脚1 (PGD/RST_B) 保持低电平、输出电压 如下图所示。

电阻值通过 "TPS546D24A_TPS546B24A_TPS546A24A_ExcelCalculator_SchematicLayoutChecklist.xlsx"计算、如下所示:

MSEL1 UP 2.37K( 实际焊接2.2K+160ohm 1%),Down 21.5K(实际 焊接 18K+3.6K 1%);

MSEL2向上打开,向下10K 1%;

ADRSEL 向上打开,向下10K 1%;

VSEL 向上打开,向下31.6K(实际 焊接 30K+1.5K 1%)

请帮助我找出问题所在。以下附件 是相关电路和 xlsx 文档。

您的答案将非常有帮助。

e2e.ti.com/.../6431.SCH.pdfe2e.ti.com/.../TPS546D24A_5F00_TPS546B24A_5F00_TPS546A24A_5F00_ExcelCalculator_5F00_SchematicLayoutChecklist_5F00_20200626.xlsx