你好。

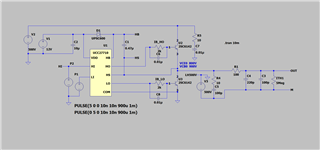

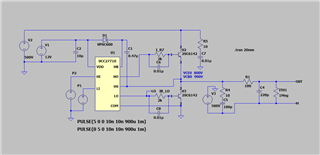

我正在考虑使用 UCC27710的斩波输出电路。

开关元件使用双极晶体管来降低噪声。

我正在使用。 当您操作它时、基极电流将从中间下降、

输出电压将下降。

UCC27710的 HO 输出端是否有电流限制电路? 如果有的话

上限电流是多少?

谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

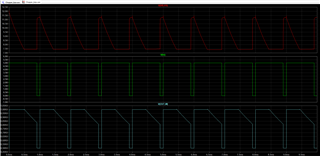

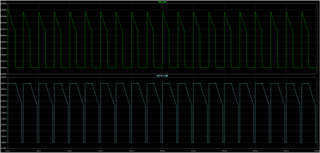

感谢您的澄清。 HI 输入脉冲保持高电平多长时间? 我提出的原因是 HO 输出由从 HB 连接到 HS 的外部电容器偏置、而电容器依靠低侧晶体管的开关在每个周期进行再充电。 可能会发生的情况是、电容器放电至 HB-HS UVLO 阈值以下、因此在周期完成前 HO 下降至0。 我建议使用差分探针测量 HB-HS 电压电平、以检查电压电平是否低于 HB-HS UVLO 阈值。

关于电流限制问题、该驱动 器旨在驱动容性负载、因此能够提供0.5A 拉电流、1.0A 灌电流的峰值电流。 输出端直流电流的绝对最大规格为 150mA。 然而、由于电容器偏置、驱动器将放电并最终达到 UVLO、因此在 HO 处驱动器无法100%打开时间。

输出电流受驱动器输出级、FET 内部电阻和任何添加的栅极电阻器(更多信息、请访问 :https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1105985/faq-ucc27614-gate-driver-peak-current-considerations)的限制。

此致、

Leslie

你好。

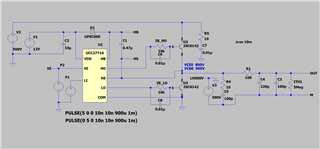

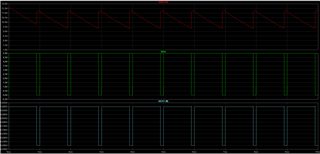

非常感谢您的快速回复。 HI 输入脉冲(图中为绿色)为900uS。 如答案中所示、HB 和 HS 之间(图中为红色)在500uS 时低于 UVLO 阈值。 我了解电流限制。 作为改进计划、我将晶体管的基极电阻从2kΩ Ω 更改为10kΩ Ω、因为输出电流为1mA。 结果显示在随附的图表中。 HB 和 HS 之间的下限电压为9V 或更高、输出电压未下降。 如果没有问题、我将保留0.47uF 的 C1并采用该电路。 如果您有任何意见、请告诉我。 非常感谢。