条件:TI UCC24624 EVM

修改点:更新了 MOSFET

电源条件:VO (MAX) 23.5V/ IO (MAX) 11.2A

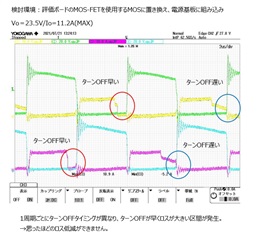

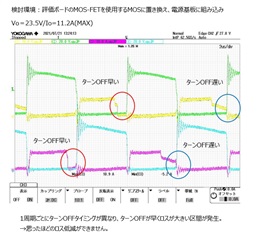

原始波形如下所示、我可以看到关闭时序使体二极管损耗更大。

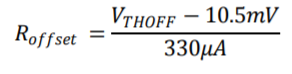

然后、我的客户调整了 Roffset 值(VSS 终端)。 通过改变 Roffset 值、它提高了效率。

我可以理解关闭是因为提前计时、但请告诉我为什么2个中的1个关闭时间更早?

另一个问题是将 VSS 端子电阻增大到过高会产生什么副作用?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

条件:TI UCC24624 EVM

修改点:更新了 MOSFET

电源条件:VO (MAX) 23.5V/ IO (MAX) 11.2A

原始波形如下所示、我可以看到关闭时序使体二极管损耗更大。

然后、我的客户调整了 Roffset 值(VSS 终端)。 通过改变 Roffset 值、它提高了效率。

我可以理解关闭是因为提前计时、但请告诉我为什么2个中的1个关闭时间更早?

另一个问题是将 VSS 端子电阻增大到过高会产生什么副作用?

大家好、Hironori

我不清楚你的问题。

Ω 电阻器 Roffset 专为编程关断阈值 VTHOFF 而设计、可实现最佳效率性能、建议外部失调电阻器值小于212 μ F。

如果 Roffset 过大、关断阈值较高、则可能会有负电流流经 SR MOSFET、这会导致 SR MOSFET 从漏极到源极的电压应力。

因此、SR 需要注意两点:

SR MOSFET 的热性能和效率

2. 从 SR MOSFET 漏极到源极的电压应力。

云生

Q1)请告诉我快速栅极关断计时→缓慢关断计时、但在增大负载电流时会交替的机制。

如果栅极关断时序始终快速、寄生电感会导致高漏源电压

我可以看到 Vthgoff 电压快速上升和下降。

您可以看到、您可以调节 VSS 端子上的电阻以升高 Vthgoff。

我不知道在快到慢到慢关闭时间之间交替的机制。

Q2)

当漏极电流下降时、栅极电压会降低以保持 Vthreg 电压。

在调整 VSS 引脚时、是否正确地认识到 Vthreg 电压不会改变、而只会改变 Vthgooff?

Q1:UCC24624具有比例栅极功能、当 SR 电流接近0V 时、栅极电压可以降低、然后关断速度快。

在 UCC24624中、比例栅极驱动器在 SR 导通时间的前半部分被禁用、具体取决于前一个周期的 SR 导通时间。 因此、栅极驱动电压仅在 SR 电流下降沿期间降低、这有助于保持低导通损耗。 如果 SR 压降在前一个周期导通时间的90%内未达到比例栅极驱动阈值 VTHPGD_LO、则强制栅极驱动电压降低。 比例栅极驱动器现在尝试将 VDS 调节至–100mV (VTHPGD_HI)。 这进一步确保了高 di/dt 条件下的快速关断速度。

Q2:是的、Vthreg 不随不同的 Roffset 而变化

云生