大家好、

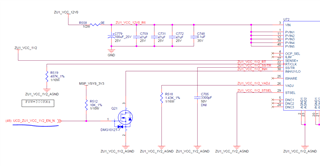

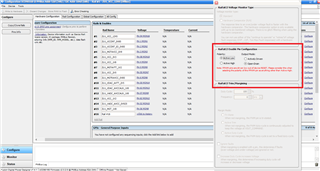

我们在电路板中使用了 UCD90160A 电源序列发生器。 我们已使用 FPWM2/GPIO6引脚来启用需要启用低电平有效的稳压器之一(默认情况下应为高电平、保持稳压器关闭、并应在根据序列启用稳压器的同时变为低电平)。 当我尝试在 Fusion Digital Power Designer 工具中将引脚设置为低电平有效时,它会向我显示一条注释:FPWM 引脚在复位后驱动为低电平,如下所示

稍后、我了解到 FPWM 引脚在复位时被驱动为低电平。 我的问题是:

1. 如果在 FPWM2/GPIO6引脚上采用低电平有效配置,这会影响我的电源定序,如果器 件 V33A 和 V33D 保持高于 VRESET (最大2.4V),并且器件 RESET 引脚(引脚9)保持高电平到3.3V,从而避免复位。

2.除 V33A 和 V33D 外、任何其他可能性低于 VRESET (2.4V)且 RESET 引脚为低电平、因此 FPWM 引脚会进入 RESET 状态(低电平)并影响定序。

提前感谢、

Kiran