主题中讨论的其他器件: UCC27211

大家好、团队成员

我们的客户在其 BBU 项目中使用 UCC27211A、我们的器件在正常情况下工作正常。

但是当他们尝试将 Li 引脚永久拉至高电平时,他们发现 LO 引脚将 变为低电平。

我们 的器件是否具有任何保护功能、以确保 LO 引脚不会永久 拉高?

您能提供一些建议吗?

谢谢。

毛利

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好、Richard

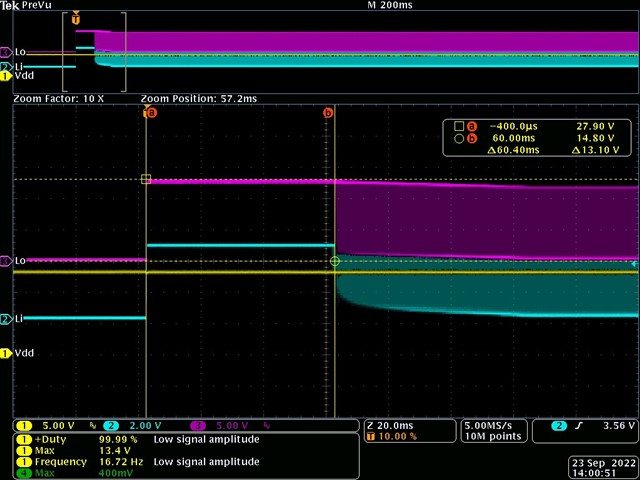

请检查波形、谢谢。

你(们)好、Richard

请检查波形。

如您所见、 当我们首先应用 VDD 时、波形返回正确。 请参阅下图以获取参考

因此、问题似乎与 电源序列有关。

客户更愿意向我们提出以下问题:

1、如果我们同时应用 VDD 和 Li、那么我们的 LO 输出为何不能跟随 Li?

2、当问题发生时、LO 输出可以恢复正常、而 PWM 输入到 Li。 为什么? 上升/下降沿似乎可以使 LO 恢复正常?

客户在 BBU 项目中用于服务器系统、因此 可靠性非常重要。

他们担心我们的器件上存在任何其他风险。 所以他们需要 有关这个问题的机制。

谢谢。

毛利