大家好、团队、

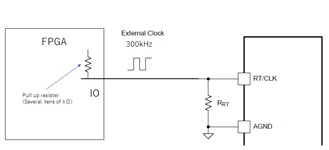

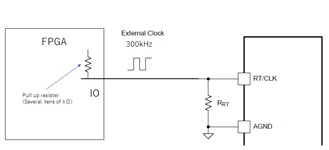

客户询问如何在 LMZ31710 RT/CLK 引脚和用于外部时钟的 FPGA IO 之间进行连接、如下所示。

他们希望在上电时使用 RT 模式、然后更改外部时钟模式。

FPGA IO 具有弱上拉电阻器(几十千欧),因此它们担心上拉电阻器会在 RT 模式加电时影响开关频率。

因此、他们想知道如何连接。 请提供建议吗?

此致、

Akihisa Tamazaki

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、团队、

客户询问如何在 LMZ31710 RT/CLK 引脚和用于外部时钟的 FPGA IO 之间进行连接、如下所示。

他们希望在上电时使用 RT 模式、然后更改外部时钟模式。

FPGA IO 具有弱上拉电阻器(几十千欧),因此它们担心上拉电阻器会在 RT 模式加电时影响开关频率。

因此、他们想知道如何连接。 请提供建议吗?

此致、

Akihisa Tamazaki

您好、Akihisa、

建议使用交流耦合电路连接 LMZ31710。 如果时钟源不可用、则需要使用 RT/CLK 电阻器正确设置频率。

从技术上讲、我们可以将时钟源直接连接到 LMZ31710 RT/CLK 引脚、但通常不建议这样做。 仅当时钟源不可用时为高阻抗 、或者 当启用 LMZ31710时、应用能够确保时钟源始终可用于 LMZ31710时、才允许直接连接。

如果启用 LMZ31710并且时钟源将 RT/CLK 引脚拉为高电平或低电平、则开关频率将无法预测。 如果时钟源变为低电平、则会拉取 RT/CLK 引脚的大量电流、因此 FSW 将非常高。 如果时钟源变为高电平、RT/CLK 引脚将不会有电流输出、因此 FSW 将真正处于低电平。

在下面的分立式交流耦合电路中、我们建议在交流耦合电容器中包含一个串联电阻器和一个肖特基钳位二极管、就像 TPSM84824EVM 上的那样。 肖特基二极管会钳制负电压、串联电阻器会限制流经二极管的电流、以保持低 Vfwd 电压。 图像。

如果您有任何其他问题、请告诉我。

Yitzhak