尊敬的团队

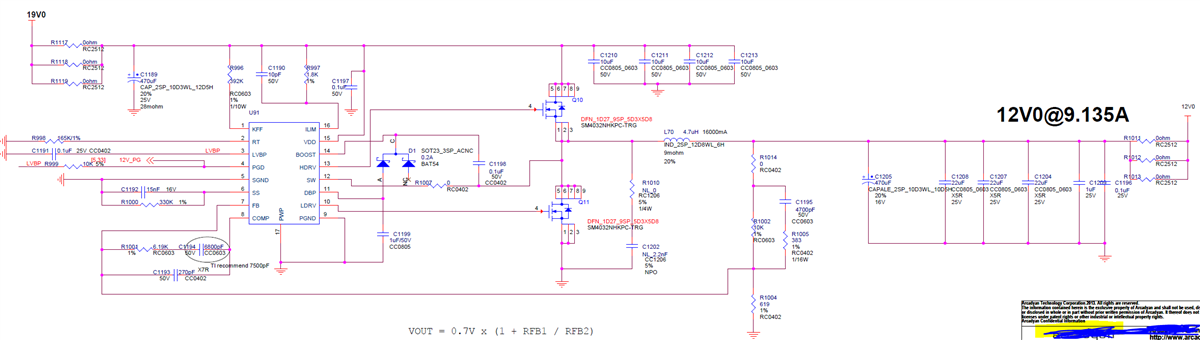

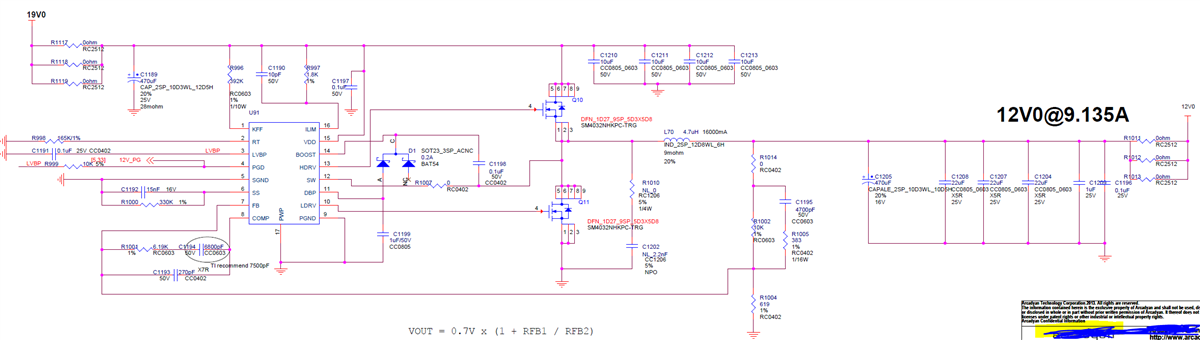

一个好消息 是、我们在客户的新项目中使用 TPS40077 (U91)进行设计。

您可以帮助查看布局吗?

e2e.ti.com/.../3618.BS72RS1400A_2D00_ZZ_5F00_20210914.brd

非常感谢

丹尼

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的团队

一个好消息 是、我们在客户的新项目中使用 TPS40077 (U91)进行设计。

您可以帮助查看布局吗?

e2e.ti.com/.../3618.BS72RS1400A_2D00_ZZ_5F00_20210914.brd

非常感谢

丹尼

丹尼

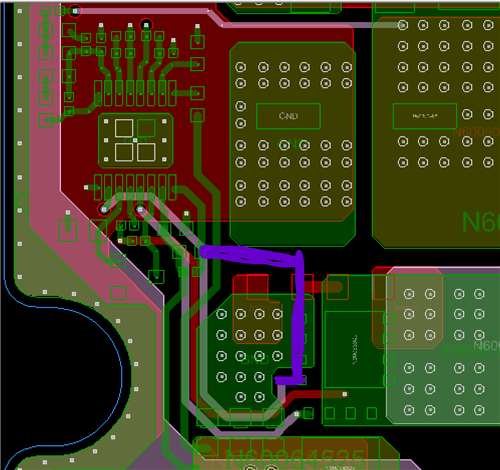

布局非常好、但有一些地方可以改进。

栅极驱动环路(LDRV 到栅极、栅源极到源极、源极到 PGND、HDRV 到栅极、栅源极到源极、 拉电流至 SW)承载高动态电流。 当电平发生变化时、它们应具有2个过孔。 我还建议他们在源极引脚下路由 LDRV 并返回 LDRV 过孔。

我还建议将 SW 网络直接路由到 HDRV 布线下方。 此外、我建议将所有这些迹线的宽度扩大到20mil 或30mil。

我还建议增加 PGND 连接、以使用至少2个通孔、甚至更好地直接连接到散热焊盘。

我建议增加用于将 DBP 电容器连接到 GND 的过孔数量。

我还建议将高侧 FET 右侧的 VIN 电容器向上移动到更靠近 FET 的位置、并将左侧的三个电容器之一移动到更靠近 FET 的位置、并从左侧提供单独的环路 电压。

否则、情况看起来不错。

你(们)好

感谢您的大力支持。

但是客户希望再次确认 一些建议。 请帮您推荐。

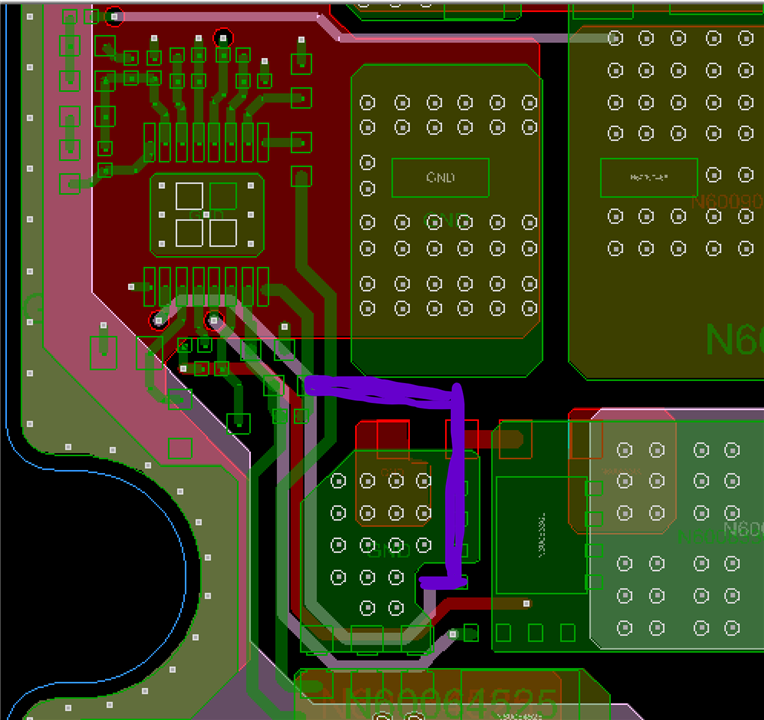

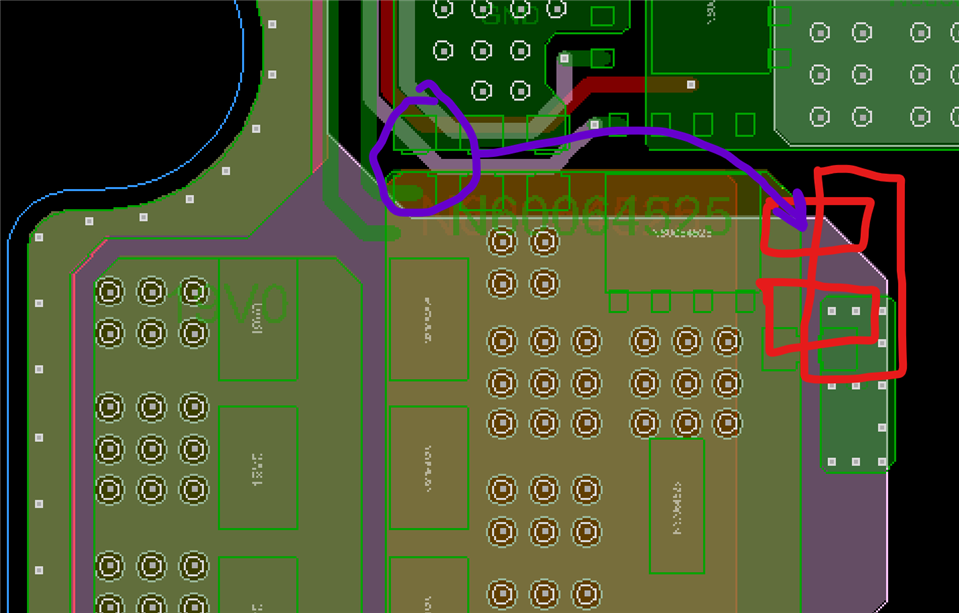

栅极驱动环路(LDRV 至门、门至源极、源极至 PGND、HDRV 至门、栅极至源极、 拉电流至 SW)承载高动态电流。 当电平发生变化时、它们应具有2个过孔。

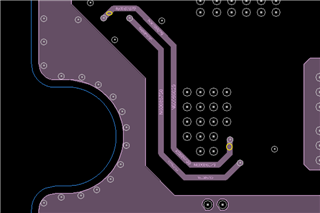

=>这2个过孔意味着:顶层需要添加一个过孔, 如下所示。

我还建议他们在源极引脚下路由 LDRV 并返回 LDRV 过孔。

=>源极引脚下 LDRV 路由的走线是否存在任何问题?

非常感谢

丹尼

是的、每次信号改变层时有两个过孔。

[引用 userid="484530" URL"~/support/power-management-group/power-management/f/power-management-forum/1038587/tps40077-layout-review/3851726 #3851726"]=>源极引脚下 LDRV 路由的布线是否存在任何问题?这不是一个主要问题、但在源极引脚下使用更少的迹线和更低的电感对 LDRV 进行布线将有助于减少开关节点 dV/dt 上升期间的低侧栅极上升。