主题中讨论的其他器件: UCC27611

大家好!

我尝试使用 GaN 型 MOSFET 实现 H 桥结构。 我使用的驱动器是 LMG1210。 我添加了原理图和波形。 我将尝试总结以下问题。

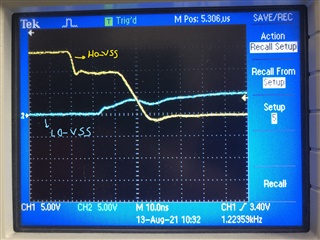

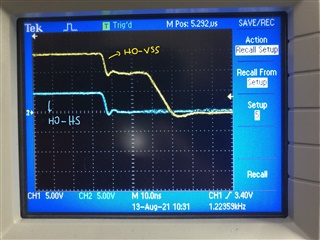

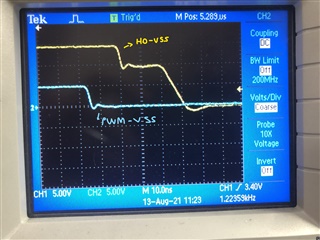

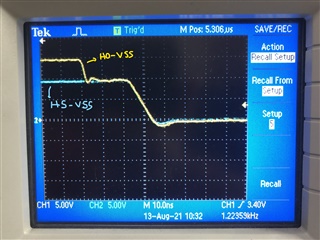

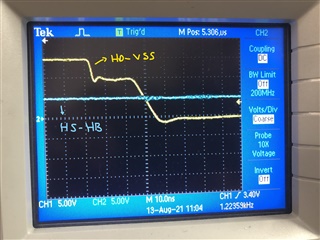

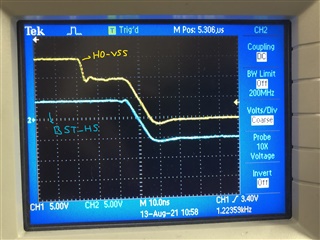

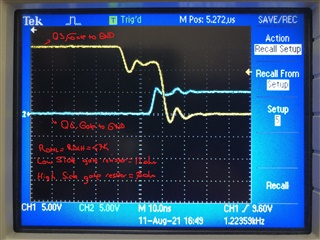

我为 DHL 和 DLH 放置47k 电阻器、为高侧和低侧栅极电阻器放置零欧姆电阻器。 47k 电阻器必须在高侧栅极的下降沿和低侧栅极的上升沿之间建立12ns 的死区时间。 高侧的源极电压将下降、直到漏极的 High_V、然后保持在那里12ns。 当低侧 MOSFET 导通时、高侧 MOSFET 看起来会完全关断。 但是,这不应该是这样的。 高侧 MOSFET 必须完全关断、然后在12ns 后、低侧 MOSFET 必须导通。

如果我在此增加4.7欧姆等栅极电阻器、即使低侧 MOSFET 导通、它也会等待一段时间使高侧 MOSFET 完全关断并发生击穿。

我在该实验中对 High_V 应用10V。 当我提供180V 电压时、有时只有高侧 MOSFET、有时高侧和低侧 MOSFET 都会烧断。 LMG1210栅极驱动器也会被销毁。

然后、我只使用了一个电阻器、而不是线圈作为负载。 除此之外、我还在高侧和低侧 MOSFET 上添加了外部续流二极管。 没有改变。 波形与以前一样。 在高侧的下降沿期间仍然存在击穿问题。

现在、我怀疑是 LMG1210。 它看起来不像预期的那样工作。 我更换了几个。 但结果始终相同。

谢谢你

e2e.ti.com/.../H_5F00_BridgeSimp.pdf

e2e.ti.com/.../H_5F00_BridgeSimp.pdf

此致。