Q1)如果您有1层外壳 PCB 示例、请分享。

数据表显示了2层示例、但我的客户将继续使用1层电路板。

Q2) https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1021108/ucc24624-roffset-question?tisearch=e2e-sitesearch&keymatch=UCC24624#

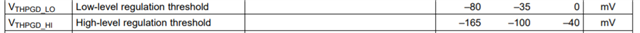

关于此主题、数据表显示-35mV = Vthpgd_low voltage

不过、我的解释是典型值为-50mV。 有何不同?

最初、我的理解来自-35mV (Vthpgd_low)。 当导通时间达到90%时、阈值在未达到–35mV (Vthpgd_low)时切换为-100mV (Vthpgd_high)。

来相应地控制栅极。 是只有两种 Vth 类型、即低电平和高电平、还是它们会有所不同?