在更改 FET 时、我们应该考虑哪些因素? 应修改哪些组件、这会如何影响我们的整体系统性能?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

在更改 FET 时、我们应该考虑哪些因素? 应修改哪些组件、这会如何影响我们的整体系统性能?

设计人员可能需要更改 FET 的原因有很多、例如器件短缺、系统规格变化或尝试通过更改开关频率等规格来提高系统性能。 但是、当设计人员在不修改栅极驱动电路的情况 下交换 FET 时、由于 FET 器件型号之间的动态特性(RDSON、CISS、COSS、内部 RG)发生变化、他们在不知情的情况下可能会导致应用性能发生急剧变化。 众所周知、栅极电阻器对于限制栅极驱动路径中的噪声和振铃至关重要、但您是否知道栅极电阻器的影响不止这些? 栅极电阻的变化会影响 FET 的栅极充电 电流、这会直接影响漏源极电压压压摆率和开关节点上的过冲。 更快的 dv/dt 有助于降低开关损耗、但设计人员必须将峰值开关节点压摆率限制在栅极驱动器电平转换器的最大 dv/dt 规格范围内、并将开关节点过冲限制在 FET 的击穿电压范围内。 更高的栅极电阻必然会导致开关时间更长、开关损耗增加、但开关节点过冲更低。 如果栅极电阻太小、栅极驱动器会在开关节点处受到较大过冲电压的影响、但开关速度更快。

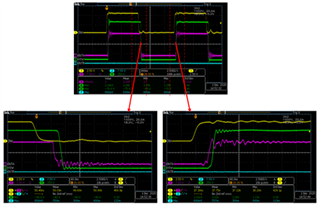

下面的数据 是 使用 高侧双脉冲测试测得的、其中 INB 在向 INA 馈入 PWM 信号时保持低电平、从而打开/关闭高侧 FET。 负载是从开关节点连接到 PGND 的电感器。 第一个脉冲在电感器中累积电流、最高达到指定 的阈值、第二个较短的脉冲仅 用于测量 FET 的导通特性。

双脉冲测试设置:

测量数据:

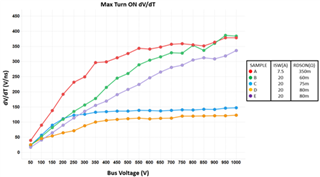

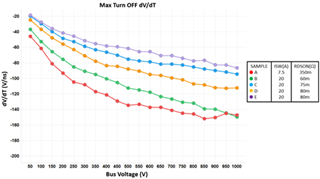

图3中的以下数据 是在室温下使用具有+4A/-8A 典型栅极驱动强度、外部栅极电阻为0欧姆的同一栅极驱动器获取的。 采用 TO-247-4封装的几个不同1.2kV SiC FET 样片在不同总线电压下的相同开关电流下使用推荐的数据表驱动电压进行了测试、可以观察到每个样片在总线电压下具有独特的峰值压摆率曲线。 这些曲线揭示了 FET 之间动态性能的巨大差异、并突出了将所有特性视为唯一的需求。 如前所述、电路设计人员必须将峰值开关节点 dv/dt 限制在栅极驱动器电平转换器电路的规格范围内。

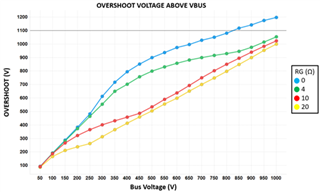

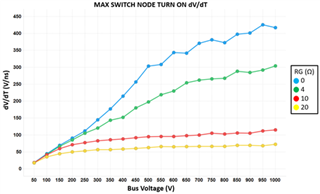

共模瞬态抗扰度(CMTI)是在设计以高开关频率运行的栅极驱动器时需要考虑的基本参数。 当开关节点的变化率高于数据表值时、驱动器可能会遇到逻辑错误、在高压摆率下、输出可能会出现高电平或低电平毛刺脉冲。 在本案例研究中、我们将研究将开关节点过冲限制为<1100V 和 dv/dt 限制为< 100V/ns 所需的栅极电阻(图4)。 我们可以看到、对于500V-700V 范围内的总线电压、较高的栅极电阻(>10欧姆)与较小的值(<5欧姆)相比、可非常有效地将 dV/dt 保持在100V/ns 附近。 电压过冲也受到外部栅极电阻的严重影响、在300-600V VBUS 范围内、我们可以看到低栅极电阻(< 5欧姆)下的过冲高达300-400V。 请务必记住、FET 在低温下的开关速度可能会更快、并且应在系统所需的温度范围内优化 RG。

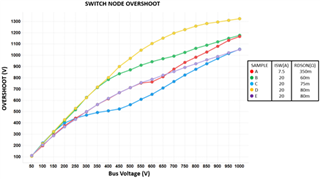

下面的图5显示了在没有外部栅极电阻的情况下、多个不同 SiC 器件型号上的各种过冲范围。 同样、每个制造商的 FET 都会产生不同程度的开关节点过冲。 开关速度更快的 FET 往往具有更大的过冲、在600V 时、测得的最大过冲为600V。 如果没有外部栅极电阻来减少过冲、则额外的600V 会导致 SiC FET 击穿、其 VDS 击穿电压为1200V。