请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS543C20 尊敬的 TI 团队:

我们在电路板中使用采用双相配置的 TPS543C20堆叠稳压器。 我们已连接数字负载以验证 PDN 特性。

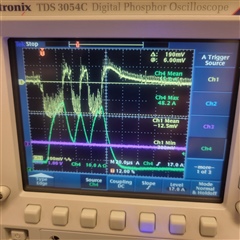

目前、在电路板上、我们禁用了从 IC、目前仅使用了1个 IC。 输出电压配置为0.8V、当我们运行高电流测试时、会观察到超过100mV 的压降。

请查找随附的图像以供参考。

这种高压降的原因可能是什么。

请提供您对同一内容的意见。

e2e.ti.com/.../TI-Regulator.pdf

谢谢、此致、

Vyshnav Krishnan