我是 Seoultech 大学的 Jaehon Kim Ph.D studeont。

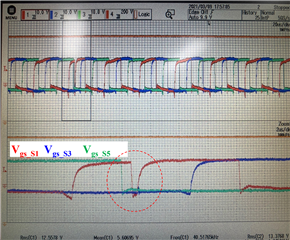

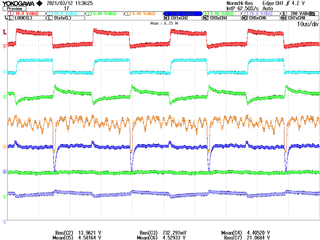

我将 ISO5852S 用于三相转换器。 但是、当栅极信号应该打开时、它突然关闭、然后打开。

请提供建议。

*条件

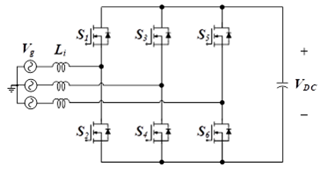

-拓扑:三相转换器

-接通电压:15V

-关断电压:-5V

- DESAT 故障功能:请勿使用(DESAT 引脚已连接至 GND)

- Situration

:所有开关的负荷都是0.5,每个腿都有120度相移。

当开关 S6导通时、S1的栅极信号会降至负电压并重新导通。

请告诉我如何解决这个问题。

谢谢你