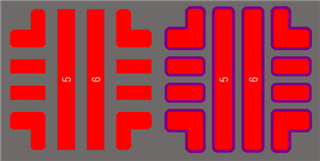

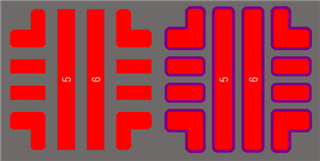

它看起来不像 TPS25947的 Altium UltraLibrarian 封装那样已经修复。 数据表显示了正确的阻焊层信息。 在 Altium UltraLibrarian 封装中、阻焊层的尺寸与铜焊盘完全相同。 下面是一些屏幕截图:

UltraLibrarian 封装位于左侧、其外观位于右侧。

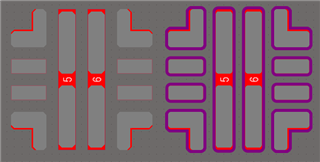

铜焊盘、背景中带有阻焊层:

仅阻焊层:

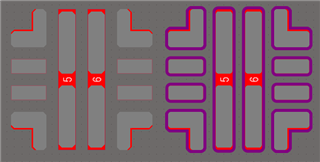

铜层、阻焊层和焊锡膏层:

Greg

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

它看起来不像 TPS25947的 Altium UltraLibrarian 封装那样已经修复。 数据表显示了正确的阻焊层信息。 在 Altium UltraLibrarian 封装中、阻焊层的尺寸与铜焊盘完全相同。 下面是一些屏幕截图:

UltraLibrarian 封装位于左侧、其外观位于右侧。

铜焊盘、背景中带有阻焊层:

仅阻焊层:

铜层、阻焊层和焊锡膏层:

Greg

您好、Kunal、

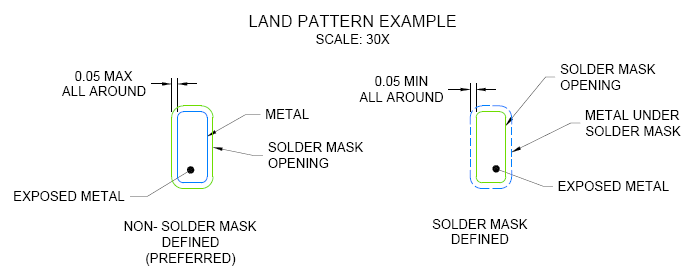

虽然从技术上讲、封装不遵循任一选项、但您可以说它遵循数据表中定义的非阻焊层。 我这么说是因为数据表显示"0.05 MAX ALL YOUT"、所以从技术上讲、0.00满足要求(但不是一个很好的使用值)。

根据数据表、定义的阻焊层需要至少0.05的重叠、但 UltraLibrarian 封装中的阻焊层和铜尺寸完全相同。

不得使用与铜焊盘大小完全相同的阻焊层。 几乎不可能将阻焊层与铜完美对齐。 您将在焊盘上有部分阻焊层。 有人告诉我 、这一微小的量会呈薄片状、您不希望在另一个焊点的其他位置形成焊层。 最好使用定义的非阻焊层、因为焊锡具有更多的表面区域可连接、从而提供更安全的连接。 这一点尤其正确、因为附件 具有多个尺寸、因为它连接到焊盘的侧面和顶部。

定义了非阻焊层 MAX 规格的原因在于、焊盘之间需要的阻焊层网数量最少。 否则、Web 可能会中断并在其他地方出现问题。

此致、

Greg

您好、Kunal、

您指的是哪种封装? RPW0010A 或 DBV0006A? 它们都直接位于 TI 网站上。 这是我下载的 DBV0006A: https://www.ti.com/product/SN6505B?keyMatch=SN6505B&tisearch=search-everything&usecase=GPN#design-development##cad-cae-symbols

我想了解 TI 定义阻焊层扩展为0的原理。 我今天早上做了一些研究、我能找到的最好的地方是一个站点(Sierra Circuits)、该站点说制造商更喜欢一对一的匹配、这样扩展就可以更改为适当的制造流程。 奇怪的是、我以前从未遇到过这种情况、但 PCB 制造商改变了阻焊层开口。

此致、

Greg

您好、Kunal、

很抱歉我 已经离开了几天。 Altium 有两个焊料和焊锡膏掩模扩展选项。 "规则"或"手册"。 当您想让用户自行决定时、应选择"规则"、因为这样设计中的所有焊盘都可以通过用户设置的全局设计规则进行控制。 如果设置为手动、则用户除了修改封装外、没有其他控制。

您曾说过"我们为客户提供了根据其要求调整遮罩的灵活性"、这对我来说毫无意义。 "规则" 选项也是如此。 我希望您的足迹开发团队能够解释他们选择一对一比率的理由。 我想我可能刚刚弄清楚了他们为什么这么做 。 PCB 制造商将标记1:1的比率、而不是布局工程师选择阻焊层扩展、而是由 PCB 制造商进行扩展。 它们具有进行更改的强大工具。 我可以看到这种方法的好处、即无论电路板的制造位置如何、一个封装就足够了。 使用规则选项时、如果 使用需要不同扩展的不同制造商、则需要生成新的光绘文件。 当比率为1:1时、可以区分1:1屏蔽扩展和针对特定尺寸的屏蔽扩展。 因此、PCB 制造商可以根据所需的尺寸扩展所有1:1比率、并保留任何非1:1的值。 如果不正确、请告诉我。

此致、

Greg